# Optimising Security, Power Consumption and Performance of Embedded Systems

#### Parisa Raimi

School of Computer Science and Electronic Engineering (CSEE)

University of Essex

This dissertation is submitted for the degree of

Doctor of Philosophy

October 2023

This thesis is a heartfelt tribute to my beloved parents, Talaat and Rahim. Their unwavering love and unyielding faith in me have been the driving forces behind my academic journey. Although they departed in 2023 and couldn't witness my attainment of a doctorate, while their absence at this milestone pains me, their memory propels me forward. I believe that their enduring blessings will continue to guide and inspire me on my future journey.

#### Acknowledgement

"All our dreams can come true if we dare to pursue them. In my opinion, hard work and determination are the essential traits of a successful researcher."

I am grateful to the many people who supported me in various ways during my Ph.D. journey. First of all, I praise and thank God for his countless blessings and for giving me the strength to accomplish this research during tough times.

This thesis will always be incomplete without expressing gratitude to my supervisor, Dr. Amit Singh. I would like to express my sincere appreciation to him for his patience, kindness, and invaluable support throughout the entire process. His guidance, tutelage, and motivation were instrumental to the successful completion of this endeavour, and I am forever indebted to him.

I am grateful to my husband and my sisters and brothers for their unwavering patience and support over the years. Without their encouragement, love, and understanding, none of this would have been possible. Their presence in my life has been a constant source of inspiration and motivation, and I am deeply grateful for their unending support.

Last but not least, I am grateful to the University of Essex for providing me with a conducive environment to carry out my studies.

"In loving memory of my dear brother's wife (Leila), whose unwavering love and everlasting contributions to my life, especially during my Ph.D. journey, fills my heart with gratitude."

#### **Abstract**

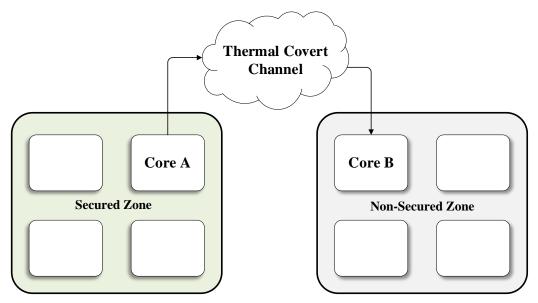

Increased interest in multicore systems has led to significant advancements in computing power, but it has also introduced new security risks due to covert channel communication. These covert channels enable the unauthorized leakage of sensitive information, posing a grave threat to system security. Traditional examples of covert channel attacks involve exploiting subtle variations such as temperature changes and timing differences to clandestinely transmit data through thermal and timing channels, respectively. These methods are particularly alarming because they demand minimal resources for implementation, thus presenting a formidable challenge to system security. Therefore, understanding the different classes of covert channel attacks and their characteristics is imperative for devising effective countermeasures.

This thesis proposes two novel countermeasures to mitigate Thermal Covert Channel (TCC) attacks, which are among the most prevalent threats. In the first approach, we introduce the Selective Noise-Based Countermeasure. This novel technique disrupts covert communication by strategically adding a selective noise (extra thread) to the temperature signal to generate more heat and change its pattern. This intervention significantly increases the Bit Error Rate (BER) to 94%, thereby impeding data transmission effectively. Building upon this, the second strategy, termed Fan Speed Control Countermeasure, dynamically adjusts fan speed to reduce system temperature further, consequently decreasing the thermal signal frequency and shutting down any meaningful transmission. This methodology achieves a high BER (98%), thereby enhancing system security. Furthermore, the thesis introduces a new threat scenario termed Multi-Covert Channel Attacks, which demands advanced detection and mitigation techniques. To confront this emerging threat, we propose a comprehensive two-step approach that emphasizes both detection and tailored countermeasures. This approach leverages two distinct methodologies for implementation, with the primary goal of achieving optimal performance characterized by high BER and low power consumption.

In the first method, referred to as the double multi-covert channel, we employ two distinct frequency ranges for the timing and thermal covert channels. Through extensive experimentation, we demonstrate that this approach yields a high BER, providing a formidable challenge to various defense strategies. However, it is noteworthy that this method may potentially lead to overheating

issues due to the increased operational load. Alternatively, our second method, the single multi-covert channel, employs a single frequency range for data transmission. Notably, this approach addresses the overheating concerns associated with the double multi-covert channel, thereby reducing power consumption and minimizing the risk of system overheating. The experimental results presented in this thesis demonstrate the efficacy of the proposed strategies. By adopting a two-different approach, we not only enhance detection capabilities but also mitigate potential risks such as overheating. Our findings contribute significantly to the ongoing discourse on covert channel attacks and offer valuable insights for developing robust defense mechanisms against evolving threats.

By providing insights into both traditional and emerging covert channel threats in multicore systems, this thesis significantly contributes to the field of multi-embedded system security. The proposed countermeasures demonstrate tangible security improvements, while the exploration of multi-covert channel attacks sets the stage for detection and defense strategies.

## **Contents**

|    | List | t of Figures                                                             | III  |

|----|------|--------------------------------------------------------------------------|------|

|    | List | of Tables                                                                | V    |

|    | Abl  | oreviations                                                              | .VII |

| 1. | Intr | oduction                                                                 | 1    |

| 1. | .1   | Background                                                               | 1    |

| 1. | .2   | Motivation                                                               | 3    |

| 1. | .3   | Research Objectives                                                      | 3    |

| 1. | .4   | Thesis Structure                                                         | 5    |

| 1. | .5   | Publications                                                             | 6    |

| 2. | Lite | erature Review                                                           | 8    |

| 2. | .1   | Overview                                                                 | 8    |

| 2. | .2   | Security In Embedded SoCs                                                | 10   |

| 2. | .3   | Embedded System Attacks                                                  | 14   |

| 2. | .4   | General Trends and Challenges                                            | 51   |

| 2. | .5   | Summary                                                                  | 54   |

| 3. | Sele | ective Noise Based Countermeasure Against Thermal Covert Channel Attacks | 56   |

| 3. | .1   | Overview                                                                 | 56   |

| 3. | .2   | Selective Noise Based Countermeasure Methodology                         | 58   |

| 3. | .3   | System and Threat Model                                                  | 62   |

| 3  | .4   | Countermeasures Against Thermal Covert Channel Attacks                   | 65   |

II Content

| 3  | 3.5         | Experimental Evaluation                                         | 71  |

|----|-------------|-----------------------------------------------------------------|-----|

| 3  | 3.6         | Summary                                                         | 77  |

| 4. | Fan         | Speed Control Based Defence for Thermal Covert Channel Attacks  | 79  |

| ۷  | <b>1.</b> 1 | Overview                                                        | 79  |

| 4  | 1.2         | Fan Speed Controlling Based Defence Methodology                 | 81  |

| ۷  | 1.3         | Experimental Results                                            | 90  |

| ۷  | 1.4         | Summary                                                         | 92  |

| 5. | Det         | ection and Defence of Thermal and Timing Covert Channel Attacks | 94  |

| 5  | 5.1         | Overview                                                        | 94  |

| 5  | 5.2         | Timing Covert Channel Attacks                                   | 96  |

| 5  | 5.3         | Methodology for Multi-Covert Channel Attacks                    | 100 |

| 5  | 5.4         | Experimental Results                                            | 112 |

| 5  | 5.5         | Summary                                                         | 115 |

| 6. | Cor         | nclusion                                                        | 118 |

| ć  | 5.1         | Future Work                                                     | 119 |

| 7. | Ref         | erences                                                         | 122 |

### **List of Figures**

| Figure 2.1 Applications domains for embedded systems.                                          | 9      |

|------------------------------------------------------------------------------------------------|--------|

| Figure 2.2 Diagram of side channel attacks.                                                    | 18     |

| Figure 2.3 Attacks on embedded systems.                                                        | 20     |

| Figure 2.4 Classification of countermeasures against power analysis attacks.                   | 25     |

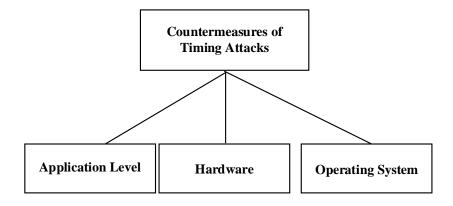

| Figure 2.5 Classification of countermeasures against timing attacks.                           | 34     |

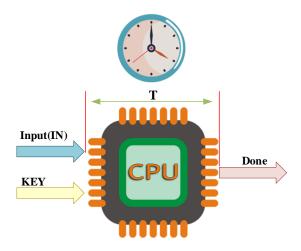

| Figure 2.6 Process of timing covert channel attacks.                                           | 46     |

| Figure 3.1 TCC communication in a multi-core system. The arrow from core A to core B           | shows  |

| that the heat flow from core A to core B.                                                      | 57     |

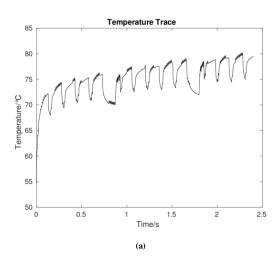

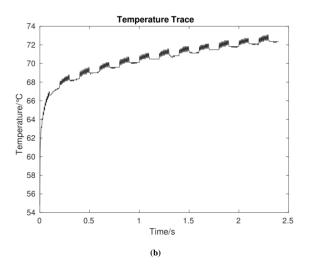

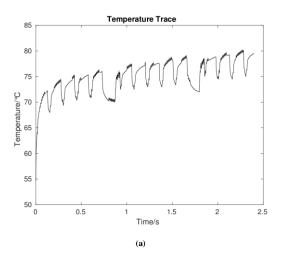

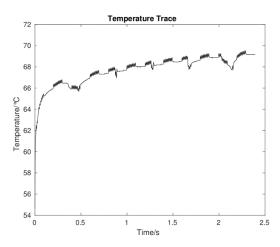

| Figure 3.2 Figure (a) and (b) are temperature traces recorded by the receiver core without and | d with |

| DVFS control, respectively.                                                                    | 59     |

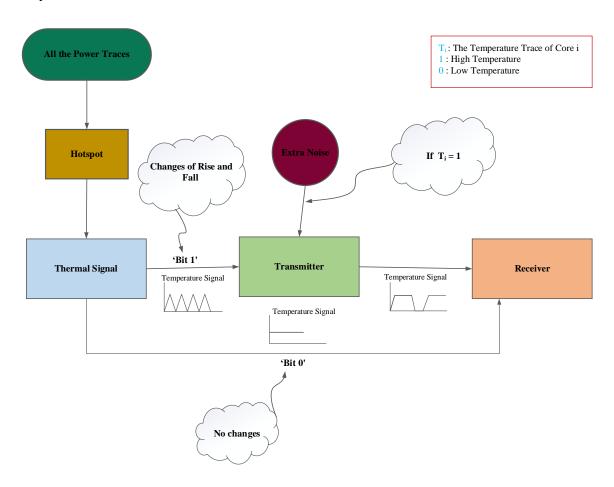

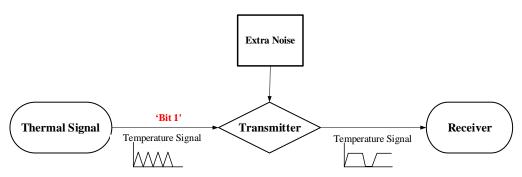

| Figure 3.3 Process of extra noise countermeasure.                                              | 60     |

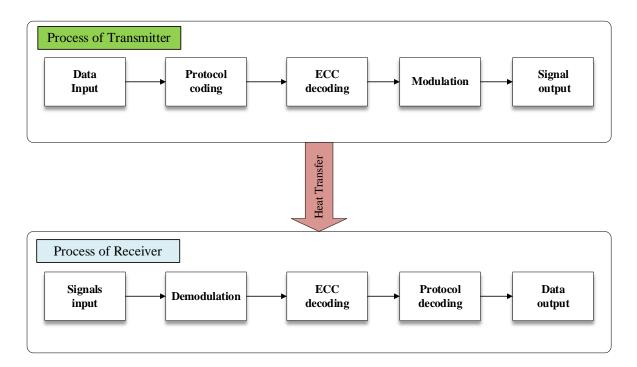

| Figure 3.4 The components and signal flow of a communication system through a thermal          | covert |

| channel: from the transmitter to the receiver.                                                 | 63     |

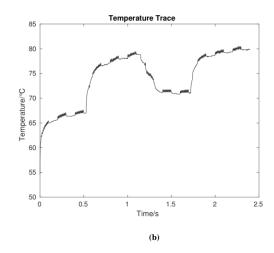

| Figure 3.5 Proposed countermeasure process.                                                    | 66     |

| Figure 3.6 Temperature timing diagrams of the receiver core without (a) and with pro-          | posed  |

| countermeasure on the transmitter core (b).                                                    | 69     |

| Figure 3.7 The process of adding selective noise.                                              | 70     |

| Figure 3.8 Outcome of the proposed selective noise-based countermeasure.                       | 71     |

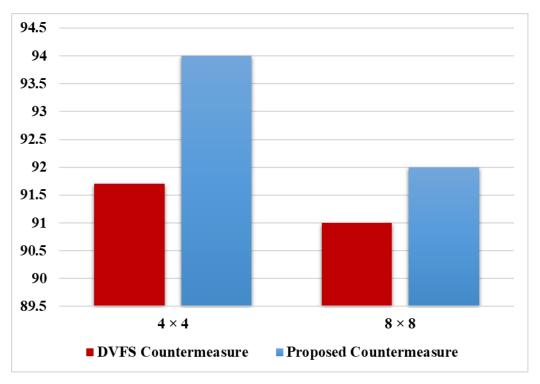

| Figure 3.9 BER with the proposed method and DVFS in different systems.                         | 74     |

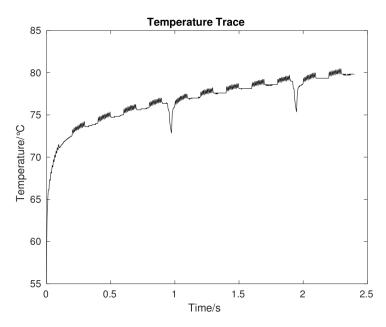

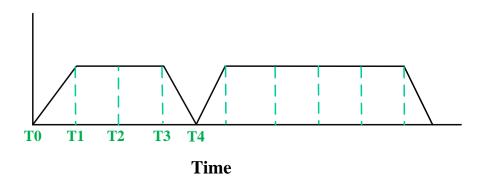

| Figure 4.1 Thermal signal with new pattern.                                                    | 80     |

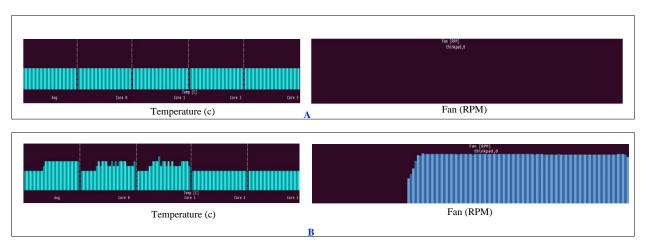

| Figure 4.2 System behaviour: (A) System without TCC, (B) System with TCC                       | 81     |

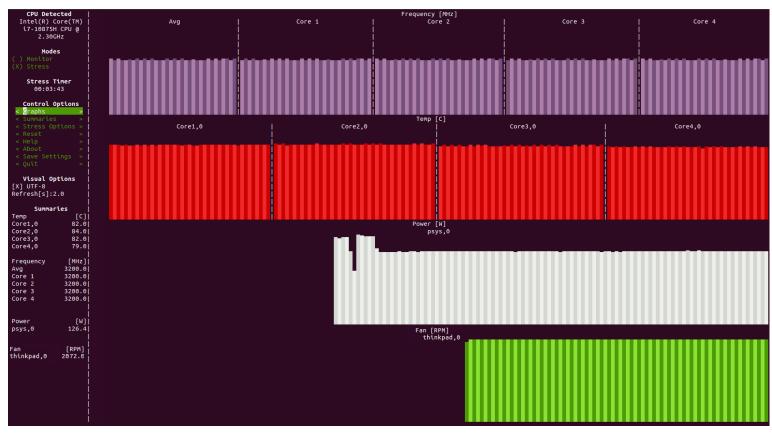

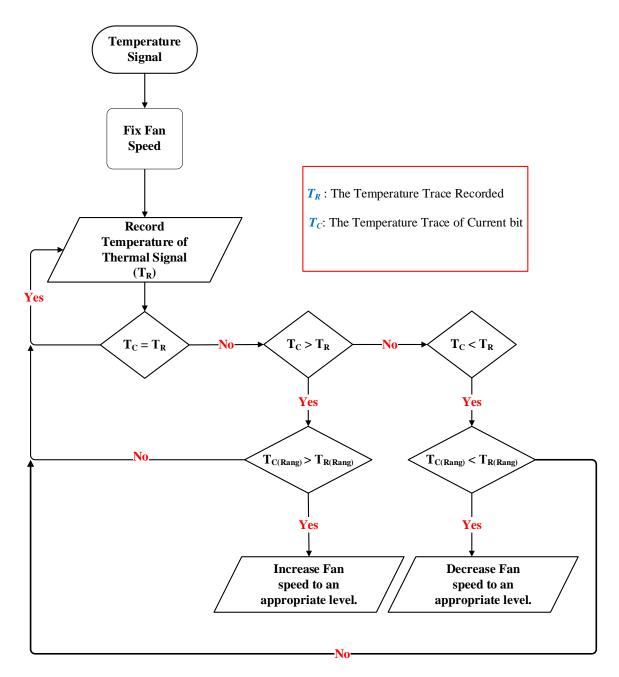

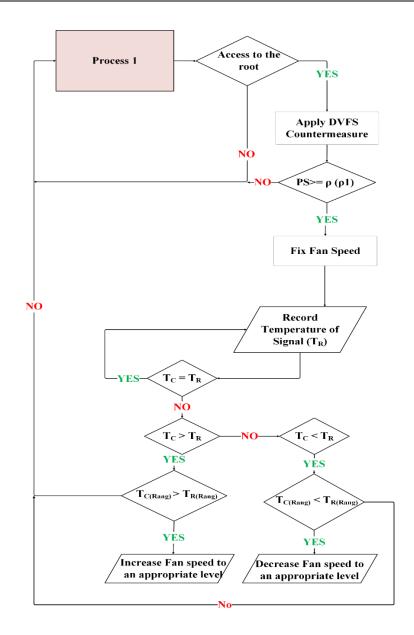

| Figure 4.3 Monitoring system behaviour.                                                        | 83     |

| Figure 4.4 The process of proposed work.                                                       | 84     |

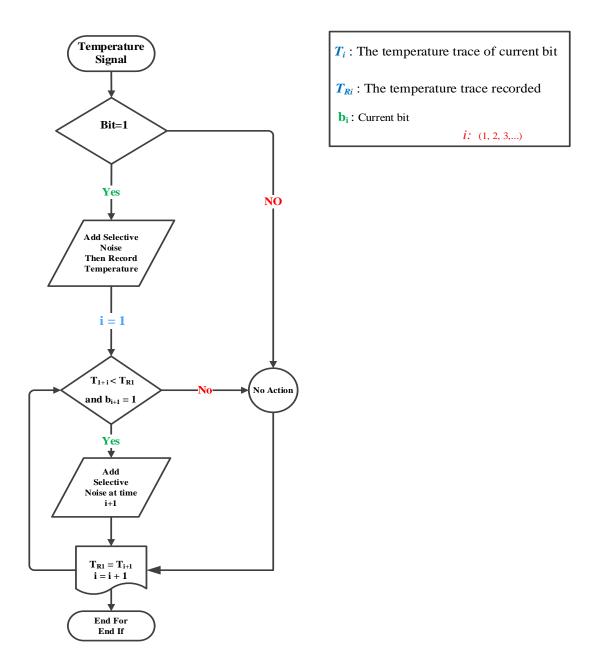

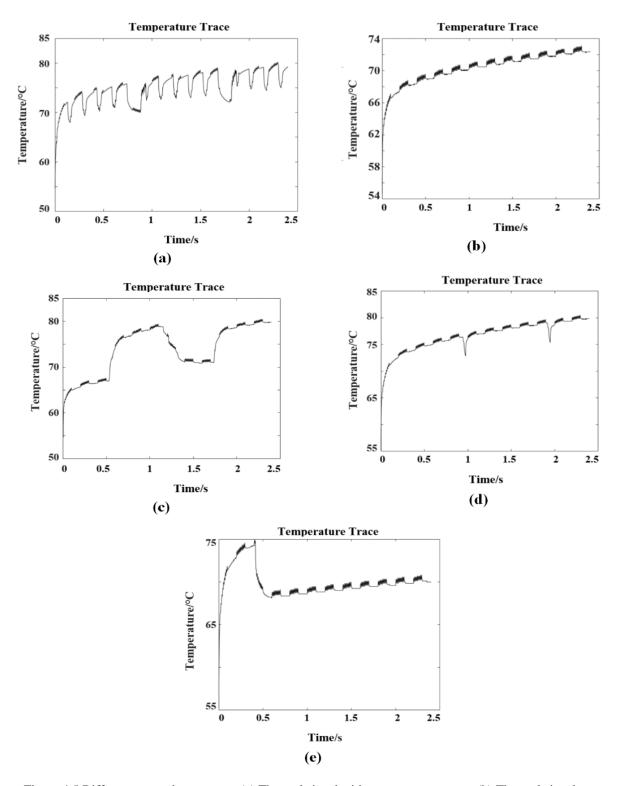

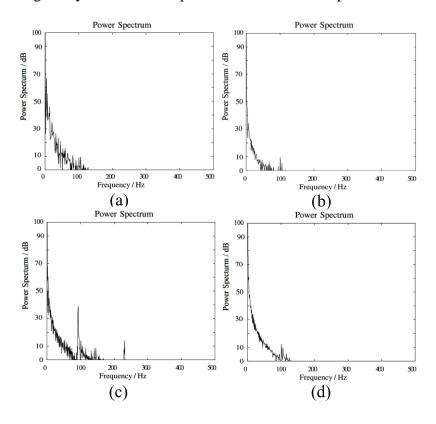

| Figure 4.5 Different research outcomes: (a) Thermal signal without countermeasure, (b) The     | nermal |

| signal with DVFS based countermeasure, (c) Thermal signal with one extra noise counterme       | asure, |

| (d) Thermal signal with selective noise-based countermeasure, and (e) Thermal signal with      | th fan |

| speed-based countermeasure.                                                                    | 87     |

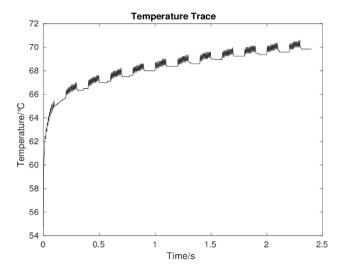

| Figure 4.6 DVFS countermeasure along with the fan speed control-based countermeasure           | 89     |

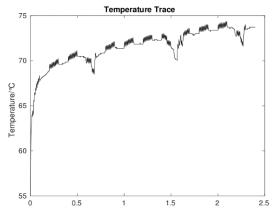

| Figure 4.7 TCC with the selective noise and fan speed control based countermeasure             | 80     |

IV List of Figures

| Figure 4.8 TCC with DVFS, selective noise and fan speed control-based countermeasure90          |

|-------------------------------------------------------------------------------------------------|

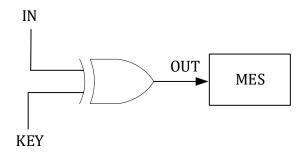

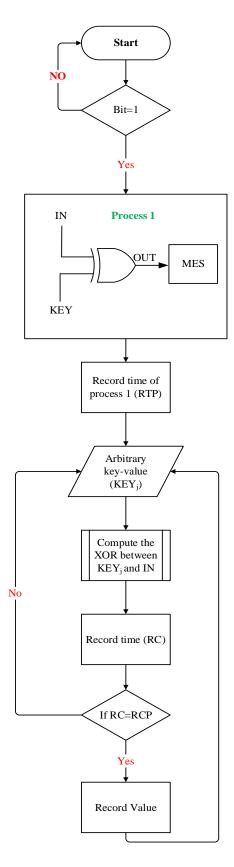

| Figure 5.1 Operation process96                                                                  |

| Figure 5.2 Process of timing attacks                                                            |

| Figure 5.3 The process of cryptographic operation                                               |

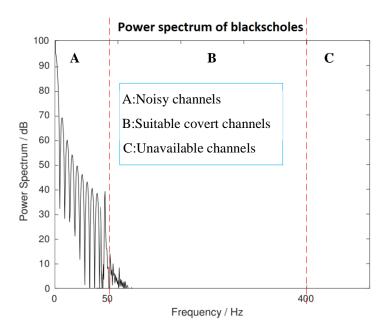

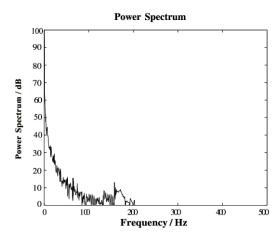

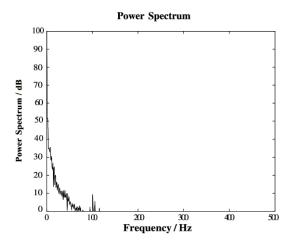

| Figure 5.4 The power spectrum of a core's temperature signal obtained when one typical          |

| application runs                                                                                |

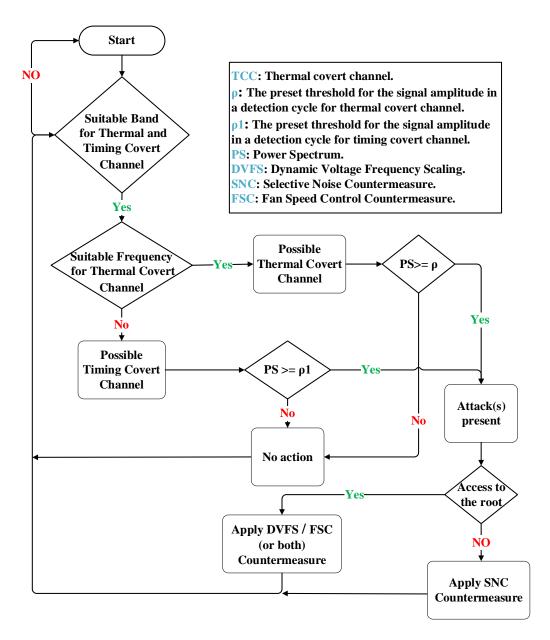

| Figure 5.5 Diagram of process of detection and defence of Thermal and Timing Covert Channel     |

|                                                                                                 |

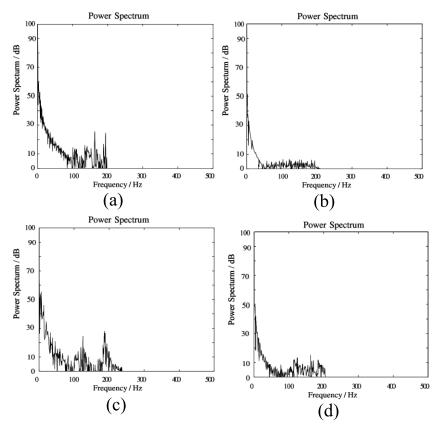

| Figure 5.6 System behaviour with double covert channels, (a) system without countermeasure, (b) |

| system with DVFS countermeasure, (c) system with Selective Noise countermeasure and (d)         |

| system with Fan Speed Control countermeasure                                                    |

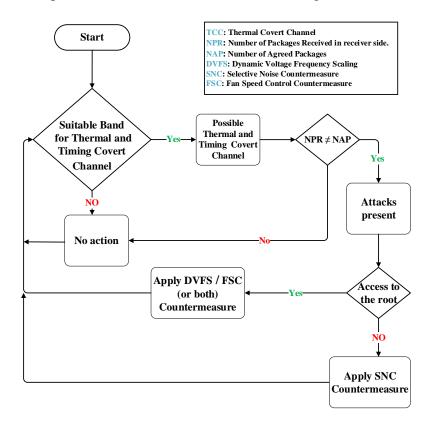

| Figure 5.7 Diagram of the process of detection and defence of Thermal and Timing Covert Channel |

| Attacks in single covert channels. 108                                                          |

| Figure 5.8 Thermal and Timing covert channel attacks are using one channel. (a) Multi attacks   |

| without countermeasure, (b) Multi attacks with DVFS countermeasure, (c) Multi attacks with      |

| selective noise countermeasure, (d) Multi attacks with Fan speed control counter109             |

| Figure 5.9 Diagram of process combine defence strategy in multi covert channels                 |

| Figure 5.10 Double covert channel with Selective Noise and fan speed countermeasure112          |

| Figure 5.11 Single covert channel with Selective Noise and fan speed countermeasure112          |

#### **List of Tables**

| Table 2.1 Security, performance and power consideration of power analysis attacks i      | n different  |

|------------------------------------------------------------------------------------------|--------------|

| research                                                                                 | 27           |

| Table 2.2 Security, performance and power consideration of electromagnetic attacks i     | n different  |

| research.                                                                                | 32           |

| Table 2.3 Security, performance and power consideration of timing attacks in differen    | it research. |

|                                                                                          | 36           |

| Table 2.4 Security, performance and power consideration of fault injection attacks in    | n different  |

| research                                                                                 | 38           |

| Table 2.5 Security, performance and power consideration of covert channel attacks in     | n different  |

| research                                                                                 | 51           |

| Table 3.1 One extra noise with different random numbers.                                 | 68           |

| Table 3.2 Configuration Details                                                          | 72           |

| Table 3.3 Detection accuracy of Pacc.                                                    | 73           |

| Table 3.4 Comparison of our experimental result with different related research          | 74           |

| Table 3.5 Experimental results with different numbers of extra noise.                    | 75           |

| Table 3.6 Consideration of various aspects in thermal covert channel attacks by existing | ng and our   |

| approaches.                                                                              | 75           |

| Table 4.1 Different states of fan speed (5°C).                                           | 85           |

| Table 4.2 Different states of fan speed (2°C).                                           | 86           |

| Table 4.3 Experimental results.                                                          | 91           |

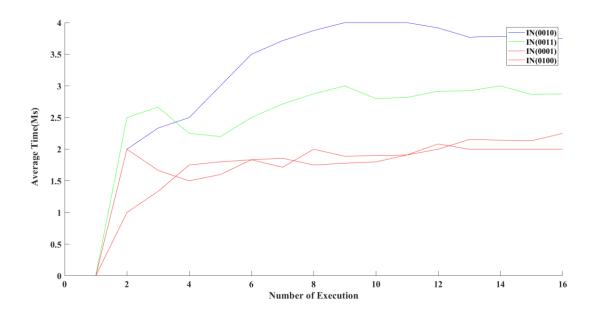

| Table 5.1 Execution time for 4 bits different input.                                     | 97           |

| Table 5.2 Predict execution time based on the random KEY                                 | 99           |

| Table 5.3 Different states of fan speed.                                                 | 103          |

| Table 5.4 Experimental results of double covert channel for timing and thermal           | 113          |

| Table 5.5 Experimental results of single covert channel for timing and thermal           | 114          |

#### **Abbreviations**

AES Advanced Encryption Standard

ARM Advanced RISC Machines

ASICs Application-Specific Integrated Circuits

ASLR Address Space Layout Randomization

AVR Advanced Virtual RISC

BER Bit Error Rate

CPA Correlation Power Analysis

CPD Change Point Detection

DPA Differential Power Analysis

DTS Digital Thermal Sensors

DoS Denial-of-Service

ECC Elliptic Curve Cryptography

ECC Error Correcting Code

EDAC Error Detection and Correction

EMI Electromagnetic Interference

EMC Electromagnetic Compatibility

EMEA Electromagnetic Emanation Analysis

EMFI Electromagnetic Fault Injection

EMFS Electromagnetic Fault Sensing

EMP Electromagnetic Pulse

FPGAs Field Programmable Gate Arrays

HSM Hardware Security Module

HSMs Hardware Security Modules

IDS Intrusion Detection Systems

VIII Abriviations

IDS Intrusion detection systems

IoT Internet of Things

IP Internet Protocol

MES Manufacturing Execution System

MITM Man-in-the-Middle

PER Packet Error Rate

QoS Quality of Service

RAM Random Access Memory

RCE Remote Code Execution

RISC Reduced Instruction Set Computer

RSAA Rivest–Shamir–Adleman Algorithm

RTOS Real-Time Operating Systems

SCAs Side-Channel Attacks

SEM Scanning Electron Microscopes

SPA Simple Power Analysis

SSL Secure Sockets Layer

STA Simple Thermal Analysis

SoC System-on-a-Chip

TCC Thermal Covert Channel

TLS Transport Layer Security

TPMs Trusted Platform Modules

XOR Exclusive-OR

# **Chapter 1 Introduction**

#### 1.1 Background

In recent years, the design objectives for numerous electronic systems have shifted towards prioritizing security, power efficiency, and performance, particularly in embedded systems. Embedded systems have become integral to various real-life applications, ranging from low-end devices like wireless handsets and networked sensors to high-end systems such as network routers and web servers. As the utilization of embedded systems continues to grow across diverse fields, addressing security becomes imperative. Balancing the enhancement of performance and security in embedded systems while maintaining low power consumption remains a significant scientific challenge for researchers. Ensuring the security of embedded systems requires the implementation of various security measures at different levels within the system's architecture. These measures include secure boot [150], data encryption, access control, secure communication protocols [151], and regular firmware updates [152]. In addition to these measures, regular security audits and testing, including automated and manual techniques such as fuzz testing, vulnerabilities in the system. Moreover, with the rising prevalence of wireless connectivity and internet access, embedded systems are becoming more susceptible to attacks. Thus, addressing security concerns

2 Introduction

is crucial at multiple abstraction levels, encompassing both software and hardware security [153]. To effectively address these security concerns, designers must consider a diverse range of techniques at various levels of abstraction. At the hardware level, secure hardware modules like Trusted Platform Modules (TPMs), Hardware Security Modules (HSMs), and secure enclaves can provide a secure execution environment [154]. On the software front, techniques such as code obfuscation, code randomization, and software diversification can mitigate the impact of side-channel attacks and logical attacks. By adopting a holistic approach to embedded system security, we can fortify these systems against potential attacks and contribute to the continued improvement of our quality of life [16].

#### 1.1.1 Performance and Power Consumption in Embedded System

Performance and power consumption are pivotal aspects of every embedded system and must be carefully considered during the design phase. These systems heavily rely on batteries for operation and are constrained by limited energy resources. Efficient power consumption is crucial for optimal embedded system functionality. Additionally, energy consumption significantly influences system performance [12]. Enhancing the performance of embedded systems has consistently presented a primary scientific challenge for researchers. Motivations for performance improvement include cost-effective hardware, reduced power consumption, an enhanced user experience, and personal satisfaction [11]. Conversely, energy consumption plays a vital role in the design of every electrical and digital system [15-17]. Hence, multi-core technology extends to embedded systems, offering the potential for achieving both high performance and low power consumption [14-13]. A brief comparison between single-core and multi/many-core systems underscore the benefits of the latter in meeting the high-performance requirements of complex embedded software. This is primarily due to the power consumption and radio frequency effects in single-core systems, whereas multi/many-core systems operate at lower frequencies. As technology advances and the demand for high performance increases, the utilization of multiple cores or different types of cores within the same chip area has experienced exponential growth [8].

Motivation 3

#### 1.2 Motivation

The escalating sophistication of electronic systems, particularly embedded systems, has paralleled an increase in their vulnerability to security threats. Side channel and covert channel attacks represent some of the most insidious risks, exploiting the unintended leakage of information through the physical operation of devices. These attacks are capable of extracting sensitive data, such as cryptographic keys, by analyzing power consumption, electromagnetic emissions, or even acoustic signals, underscoring a critical security flaw in the design of these systems. The omnipresence of embedded systems in critical sectors—automotive, healthcare, defense, to name a few—amplifies the urgency to fortify their security. The challenge is not trivial; it demands a multifaceted strategy that addresses not just the immediate vulnerabilities but also anticipates future threats. The goal is to develop resilient systems that maintain their integrity and functionality, even in the face of sophisticated attacks. This calls for innovative countermeasures that optimize security without compromising on performance or power efficiency, a balance that is crucial for the sustainability and reliability of embedded systems.

#### 1.3 Research Objectives

The overarching aim of this research is to redefine the security paradigm of embedded systems. By focusing on mitigating the risks posed by side and covert channel attacks, this work seeks to establish a new benchmark for security, performance, and energy efficiency in multicore environments. To achieve this, the study is structured around several core objectives:

- Design a methodology that can effectively counter covert channel attacks launched simultaneously from various systems or devices, ensuring robust protection across complex scenarios.

- Aim: Design and implement a methodology to counteract covert channel attacks from multiple systems or devices effectively.

- Quantifiable goal: Develop a countermeasure that reduces the success rate of covert channel attacks by at least 94%, as measured in controlled environment simulations.

- 2. Develop a methodology to defend against thermal covert channel attacks with significantly reduced power consumption and an exceptionally high bit error rate, making information extraction virtually impossible.

4 Introduction

Aim: Construct a defense mechanism against thermal covert channel attacks that significantly lowers power consumption.

- Quantifiable goal: Achieve a reduction in power consumption by 20% compared to current standards without compromising the defense mechanism's effectiveness, alongside increasing the BER to 95% or higher, making data extraction highly impractical.

- 3. Designing a comprehensive detection framework capable of identifying covert channel attacks while offering an approach to system security.

- Aim: Design a comprehensive detection framework capable of accurately identifying covert channel attacks, integrating this framework into system security measures.

- Quantifiable goal: Implement a detection system with at least 94% accuracy in identifying different types of covert channel attacks.

This study introduces novel countermeasures against thermal and timing covert channels, offering a more secure and efficient solution for the security of multi and many-core systems. The research contributes significantly to the advancement of embedded systems, addressing critical challenges related to security, power consumption, and performance.

#### 1.3.1 Key Contributions

- Introducing novel countermeasures against thermal and timing covert channels, leading to high improvement in overall security posture compared to existing solutions.

- Achieving a low power consumption for thermal attack defence compared to baseline methods, demonstrating significant advancements in energy efficiency.

- Establishing a comprehensive detection framework with high accuracy, providing valuable insights for proactive system security management.

Thesis Structure 5

#### 1.4 Thesis Structure

The structural layout adopted in the remainder of this thesis is as follows:

**Chapter 2:** Chapter 2 presents an overview of covert channel attacks and security of multi/many-core systems. This chapter presents the weakness of security and performance of these systems and the importance of them for any device or system. Furthermore, general trends and challenges in embedded systems have been discussed.

**Chapter 3:** Chapter 3 explores a new countermeasure against thermal covert channel attacks called selective noise-based power-efficient and effective countermeasures proposed to improve the security of the systems.

**Chapter 4:** In this chapter, a specific countermeasure fan speed control-based defence, is introduced on top of previous work (selective noise-based countermeasure) to improve the security of the system and decrease power consumption. We also presented the combination of the different countermeasures to check the behaviour of the system.

**Chapter 5:** In the continuum, another covert channel attack is presented (Timing covert channel attacks). We analyse the behaviour of the frequency of the system and detect and fight any possible timing attacks, find the relationships between these attacks and thermal covert channel attacks, and a muti-cover channel attack is introduced. Modifying defence methods suggested in Chapter 3 and Chapter 4, tried to fight this type of attack.

**Chapter 6:** This chapter concludes by summarising the contributions detailed in the thesis. Finally, the future of research in the field of covert channel attacks which this thesis will play is highlighted.

6 Publications

#### 1.5 Publications

The contribution of each chapter has been published as following papers during the time duration of this doctoral thesis:

- Chapter 2: Rahimi, P., Singh, A.K., Wang, X. and Prakash, A., 2021, December. Trends and challenges in ensuring security for low-power and high-performance embedded socs. In 2021 IEEE 14th International Symposium on Embedded Multicore/Many-core Systems-on-Chip (MCSoC) (pp. 226-233). IEEE.

- Chapter 3: Rahimi, P., Singh, A.K. and Wang, X., 2022. Selective noise based power-efficient and effective countermeasure against thermal covert channel attacks in multi-core systems. Journal of Low Power Electronics and Applications, 12(2), p.25.

- Chapter 4: Rahimi, P., Singh, A.K. and Wang, X., 2022, October. Fan Speed Control Based Defence for Thermal Covert Channel Attacks in Multi-Core Systems. In 2022 29th IEEE International Conference on Electronics, Circuits and Systems (ICECS) (pp. 1-4). IEEE.

- Chapter 5: Rahimi, P., Singh, A.K. and Wang, X. Detection and Defence of Thermal and Timing Covert Channel Attacks in Multi-core Systems. Under Review.

# Chapter 2

# Literature Review

#### 2.1 Overview

Embedded systems are an integral part of modern technology and can be found in a wide range of applications, such as home appliances, medical devices, and automobiles. These systems combine hardware and software to perform specific functions with real-time constraints [1]. Figure 2.1 demonstrates that embedded systems can control many common devices. A System on Chip (SoC) is a single-chip design that includes a CPU, peripherals, and sometimes memory for a computer system. Unlike traditional designs, this configuration does not feature a general-purpose bus, thus limiting its ability to interface with additional random devices. Instead, all the pins on the device are dedicated to built-in peripherals, with the manufacturer typically setting the maximum number of devices that a single SoC can support at any given time. SoC solutions offer several advantages, including reduced power dissipation, minimized chip interconnects, and decreased device size [47].

Despite their importance and widespread use, modern embedded systems are also vulnerable to security threats. These threats can range from individual systems, such as smart cards, wireless handsets, and networked sensors, to more complex connected systems, such as firewalls, network routers, servers, and gateways [43]. Therefore, it is crucial to increase the number of embedded

systems equipped with high-security features to protect against potential adversaries. Various types of attacks can threaten embedded SoCs, including logical and software attacks, as well as physical and side-channel attacks. In this study, we focus on examining covert-channel attacks more closely. Side-channel attacks exploit weaknesses in the physical implementation of a system, such as electromagnetic radiation or power consumption, rather than software vulnerabilities. These attacks are particularly concerning as they can compromise system security without being detected by traditional security measures. Therefore, developing countermeasures and strategies to mitigate the risk of side-channel attacks on embedded systems is essential [2].

Furthermore, embedded systems have become increasingly important in today's world due to their ability to control various common devices. They are designed to execute one or more assigned functions with real-time constraints, integrating hardware and software into a complete device or system. This integration of necessary chips and parts into a single chip facilitates the execution of applications or programs by loading them into chip memory or off-shelf components. Researchers have, therefore, focused on improving the performance and security of embedded systems while minimizing power consumption. In this chapter, we aim to examine all these issues more closely, specifically focusing on secure, low-power, and high-performance embedded systems. By doing so, we hope to provide valuable insights that can help advance the field of embedded systems and ensure the security and reliability of these critical components in modern technology [43].

Figure 2.1 Applications domains for embedded systems [47].

The content of this chapter has been published in "Trends and Challenges in Ensuring Security for Low-Power and High-Performance Embedded SoCs", [107].

10 Introduction

#### 2.2 Security In Embedded SoCs

Embedded systems have become ubiquitous in our daily lives, and their importance is undeniable. However, with the increasing reliance on these systems, concern for security has also escalated. Embedded systems are utilized for storing, processing, and transmitting sensitive data in various computing systems, including mobile phones, airplanes, smart cards, medical equipment, network appliances, automobiles, and digital services [2]. The vulnerability of embedded systems to security threats has increased due to their wireless connectivity and internet connections. The need for security in embedded systems is not a new issue but has become more critical than ever. To ensure the security of embedded systems, it is crucial to consider security measures at multiple abstraction levels, including both software and hardware security. Simply focusing on one aspect of security may not be enough to provide complete protection in embedded systems. Therefore, it is necessary to develop secure embedded systems that can withstand various security threats. This involves ensuring that the hardware and software components are designed to provide a high level of security. Additionally, security measures should be implemented throughout the entire development process of an embedded system, including design, implementation, and testing. The security of embedded systems should be continuously monitored and updated to ensure protection against emerging threats [4].

Embedded systems have evolved into an integral part of modern life, permeating various aspects of our daily routines. Their importance is undeniable as they facilitate critical functions in numerous devices, such as mobile phones, airplanes, smart cards, medical equipment, network appliances, automobiles, and digital services [2]. As we become increasingly reliant on these systems, the issue of security has taken center stage, with escalating concerns over safeguarding sensitive data. The vulnerability of embedded systems to security threats has been exacerbated by their wireless connectivity and internet access. This integration into interconnected networks makes them susceptible to potential breaches, raising the urgency to address security concerns. While the need for security in embedded systems is not a novel problem, it has reached a tipping point in its significance [108]. Securing embedded systems requires a comprehensive approach, encompassing multiple abstraction levels and focusing on both software and hardware security. Merely emphasizing one aspect of abstraction may not be sufficient to guarantee complete protection. Hence, the challenge lies in developing embedded systems that can effectively

withstand a myriad of security threats. Achieving robust security involves designing both hardware and software components with a high level of protection in mind. A holistic approach must be taken throughout the entire development process, encompassing design, implementation, and testing phases. Incorporating security measures early on ensures potential vulnerabilities are addressed before they become critical issues. Moreover, the journey towards secure embedded systems does not end with development; it is an ongoing process that demands continuous monitoring and updates to counter emerging threats [108]. Regularly assessing the security posture of these systems helps identify and rectify any potential weaknesses that might arise over time.

#### 2.2.1 Weaknesses in Embedded Systems

Weaknesses in the embedded systems occur because of the following reasons:

- Network connectivity: The rise of network connectivity in embedded systems has increased the risk of vulnerability to network attacks. As more embedded systems become equipped with wireless network connectivity, the potential for network attacks to exploit vulnerabilities in these systems also increases [10]. Network security has been a longstanding issue, as computer networks offer a wide range of coverage and use, thus providing an attractive target for attackers. One challenge in securing network-connected embedded systems is that the network attack surface is often much larger than the local access network [11]. This means that attackers have more potential entry points to exploit vulnerabilities in the system. Furthermore, since many embedded systems are designed to be small and lightweight, they may have limited resources available for implementing strong security measures, such as encryption or access control. To address these challenges, it is important to carefully design and implement security measures that can effectively mitigate the risks associated with network connectivity. This includes strong authentication and encryption mechanisms, limiting access to sensitive data, and implementing intrusion detection and response systems to detect and respond to attacks [12]. Therefore, the rise of network connectivity in embedded systems has increased the potential for vulnerability to network attacks. Careful design and implementation of security measures are necessary to minimize these risks and ensure the security of these systems [18].

- **Dynamic and configurable environment:** Embedded systems are often deployed in dynamic and configurable environments, presenting unique security challenges. In these

12 Introduction

environments, the operating conditions of the system can change frequently and unpredictably, potentially impacting the effectiveness of security measures. For instance, an embedded system in an industrial setting may need to adapt to variations in temperature, humidity, and other environmental factors that could affect its performance. Similarly, an embedded system in a smart home or office might need to adjust to changes in the number and types of devices connected to the network [10]. To secure these systems effectively in such dynamic environments, it is crucial to implement security measures that are both flexible and adaptable. This could involve using machine learning algorithms to dynamically adjust security settings based on changing conditions, or employing virtualization technologies to isolate parts of the system, thereby preventing the spread of malware or other security threats [11]. Moreover, regularly testing and updating security measures is essential to maintain their effectiveness amidst changing conditions. This might include conducting vulnerability assessments, penetration testing, and other security audits to identify and mitigate potential weaknesses in the system [9]. Despite the challenges posed by their dynamic and configurable nature, embedded systems can maintain data integrity and confidentiality through careful design and implementation of security measures [12].

• Software induced vulnerability: Software-induced vulnerabilities represent a common concern in embedded systems, especially those that utilize third-party software. Downloading software from the internet can inadvertently introduce vulnerabilities into the system, which attackers could exploit [8]. A typical scenario involves the use of unverified third-party software, particularly risky if sourced from untrusted websites. In some instances, attackers may distribute fake versions of popular software containing malware or malicious code. Once installed, this software can facilitate attacks or enable the theft of sensitive data [9]. To mitigate the risks associated with software-induced vulnerabilities, implementing security measures that verify the authenticity and integrity of third-party software before installation is vital. Measures might include using digital signatures to confirm software authenticity and relying on secure, trusted software repositories. Additionally, regularly updating software and firmware to patch known vulnerabilities is crucial [11]. Addressing these vulnerabilities effectively reduces the risk of attacks exploiting system weaknesses. By ensuring the authenticity and integrity of

third-party software and keeping software and firmware up to date, the risk of attacks can be significantly mitigated, safeguarding the security of the system [9].

## 2.2.1.1 Weaknesses in the Performance

Weaknesses in the performance of embedded systems occur due to several reasons:

- 1. **Limited Resources:** Embedded systems are designed to operate with constrained resources, such as memory, processing power, and energy consumption. Consequently, performance issues may arise when the system is overloaded or when there is insufficient memory or processing power to handle complex tasks [157].

- 2. **Hardware Limitations:** The hardware components of embedded systems are tailored to meet specific requirements, including size, power consumption, and cost. These constraints may result in hardware that is less powerful than that found in traditional computer systems, potentially leading to performance issues [21].

- 3. **Software Complexity:** As the functionality and capabilities of embedded systems expand, so does the complexity of the software running on them. This increased complexity can complicate the optimization of performance and the identification and resolution of issues [159].

- 4. **Real-time** Constraints: Many embedded systems operate under strict real-time constraints, necessitating responses to events within specified time frames. Meeting these constraints can be challenging and may result in performance issues if not properly managed [20].

- 5. **Environmental Factors:** Embedded systems often operate in harsh and challenging conditions, such as extreme temperatures, vibrations, and electromagnetic interference. These environmental factors can adversely affect system performance and lead to failures [22].

To address these performance challenges, developers must carefully optimize their code, utilize efficient algorithms, and manage memory effectively. Employing hardware accelerators or coprocessors to offload specific tasks from the main processor can enhance performance. Moreover, selecting appropriate hardware components during the design phase is crucial. Balancing the need for power efficiency with adequate processing power and memory is a delicate task, as each embedded system has unique requirements [23]. Despite these challenges, embedded systems have achieved remarkable success in various applications due to their specialized functionality.

Engineers and developers continue to innovate, finding creative solutions to optimize performance within the constraints of limited resources [159].

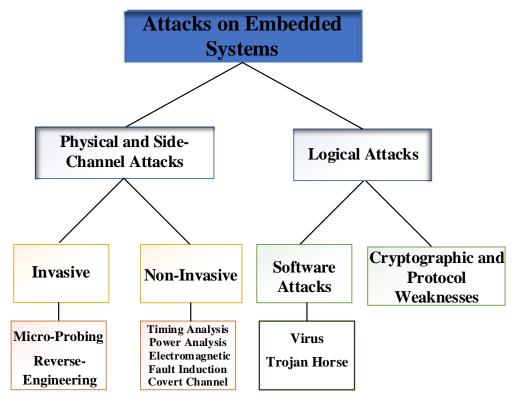

# 2.3 Embedded System Attacks

Security attacks on embedded systems can be classified by the means used to carry out the attacks. Typically, attacks on embedded systems fall into two main categories: physical and side-channel attacks (SCAs)/lateral attacks, and logical attacks, as illustrated in Figure 2.3 [4]. Physical and SCAs attacks exploit vulnerabilities in the physical implementation of the system. These attacks can be conducted through the analysis of power consumption, electromagnetic radiation, or even sound emissions from a device. On the other hand, logical attacks target vulnerabilities in the software or the logical design of the system [154].

In this section, we provide some examples of attacks against embedded systems and devices, closely examining the potential of these attacks, as well as their capabilities and implications. While this overview is not comprehensive, it is, from our perspective, quite representative and capable of covering a wide range of application domains, including hardware and software attacks.

## 2.3.1 Logical Attacks

Logical attacks typically involve sending messages to the device and then observing its behavior. The adversary's goal is often to trick the device into revealing its keys or to run malicious software. Logical attacks can be classified into two categories: 1) software attacks, and 2) attacks exploiting cryptographic and protocol weaknesses. These vulnerabilities arise from the design and algorithms of the embedded systems. The objective of these attacks is to access sensitive data, such as passwords, credit card numbers, or entire identities [5-6]. For instance:

- 1. **Code Injection:** Attackers inject malicious code into the embedded system, exploiting vulnerabilities in input validation or insecure data handling. This enables them to execute unauthorized commands or gain control over the system [160].

- 2. **Command Injection:** This attack involves injecting malicious commands into the system's input, exploiting weak input validation to execute unauthorized commands [161].

To protect against logical attacks in embedded systems, developers must adhere to secure coding practices, conduct regular security audits, and employ strong input validation mechanisms. Implementing access control and privilege separation can also limit the potential impact of

successful attacks. Additionally, timely software updates and patches are crucial to address known vulnerabilities and enhance the overall security posture of embedded systems [160].

## 2.3.2 Software Attacks

The primary goal of security design in any system is to ensure confidentiality, integrity, and availability collectively known as the CIA triad. Confidentiality aims to prevent unauthorized access to sensitive information, integrity ensures that data remains unaltered and accurate, and availability guarantees that the system is accessible and operational when needed. These three pillars are fundamental in securing any system [5]. However, in today's technology-driven world, software attacks are becoming increasingly prevalent. A software attack uses software agents like trojans, viruses, or worms to compromise a system. The goal of such an attack is to exploit vulnerabilities resulting from poor design or flawed algorithms in the embedded system [155]. Software attacks are often inexpensive to execute and do not require substantial infrastructure, unlike physical attacks. Consequently, they have become a favored method for attackers seeking unauthorized access to sensitive data or to disrupt system operations [156]. These attacks can lead to the theft of valuable intellectual property, exposure of confidential customer information, or loss of critical business operations. To prevent software attacks, it is crucial to implement robust security measures, such as access control, authentication, encryption, and intrusion detection systems. Regular security audits and vulnerability assessments are vital in identifying and addressing system weaknesses before they can be exploited. Keeping all software and systems updated with the latest security patches and updates is also critical [158]. Although confidentiality, integrity, and availability are the primary goals of any security design, the importance of protecting against software attacks has significantly increased in today's digital landscape. By adopting appropriate security measures and maintaining vigilance, businesses and organizations can defend against the harmful effects of software attacks [31].

- Below are examples of software attacks against embedded systems, each illustrating their potential, capabilities, and implications [5-6]:

- Malware Injection: Attackers compromise the security of an embedded system by injecting

malicious software, such as viruses, worms, or Trojans, potentially gaining unauthorized

control [166].

- Remote Code Execution (RCE): Vulnerabilities within the software permit attackers to

execute arbitrary code remotely, allowing them to seize control of the embedded system and manipulate its functions [162].

- Data Manipulation: Attackers alter data within the embedded system to manipulate its behavior or compromise the integrity of crucial information.

- Race Condition: Attackers exploit timing vulnerabilities in the software, leveraging concurrency issues to perform unauthorized actions [163].

## 2.3.3 Cryptographic and Protocol Weakness Attacks

With rapid advancements in communication technologies like the internet, users across various domains, including companies, home users, and government agencies—increasingly rely on digital information and data. However, the absence of adequate security measures exposes users to the risk of unauthorized access to their sensitive information, leading to fear and mistrust. Consequently, data security is paramount in the design of any system or device reliant on embedded systems. An effective strategy to mitigate this risk involves designing secure systems that prevent unauthorized access to information and safeguard the privacy of both the system and its users. Ensuring the authenticity of electronic documents and maintaining their security is also crucial. To achieve this, developing a robust security framework with cryptographic algorithms at its core is essential [167].

Cryptography, the science of secure communication, is vital for data security. Nonetheless, cryptographic and protocol weakness attacks can exploit vulnerabilities in cryptographic algorithms, including asymmetric ciphers, hashing algorithms, and symmetric ciphers, as well as in protocol stacks. The primary objectives of cryptographic attacks are to gain unauthorized access to sensitive information or to compromise a system. Thus, it is imperative to design and implement cryptographic algorithms that are resistant to attacks and capable of withstanding constantly evolving threats. These algorithms should be regularly updated to remediate any known vulnerabilities. Moreover, adopting secure protocols, such as Transport Layer Security (TLS), can further bolster data security [168].

The growing dependency on digital information and data underscores the need for stringent data security measures. Cryptography is crucial in securing data, and any system or device that relies on embedded systems must feature a design that precludes unauthorized information access, ensuring both privacy and the authenticity of electronic documents. Continuously evaluating and

updating security measures are essential practices to stay ahead of evolving threats [31].

To counter cryptographic and protocol weakness attacks, embedded systems should employ robust and correctly implemented cryptographic algorithms, secure key generation and management, and routinely update software and firmware to address known vulnerabilities. Additionally, utilizing secure communication protocols and sidestepping known vulnerabilities can significantly improve the security of embedded systems against these types of attacks [169].

## 2.3.4 Physical and Side-Channel Attacks

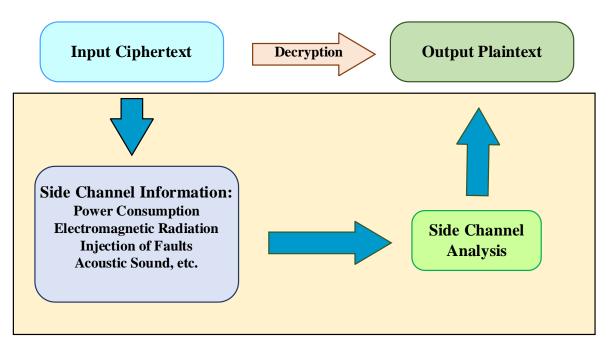

Physical and side-channel attacks are methodologies that exploit a system's performance or discern characteristics of its performance. Physical attacks, also known as invasive attacks, involve direct tampering with the system or device. Conversely, non-invasive attacks, commonly referred to as side-channel attacks, indirectly exploit the system's performance without physical interference. These attacks leverage the monitoring and analysis of the system's electromagnetic emissions, power consumption, or other external indicators to extract sensitive information [170]. Examples of non-invasive attacks include power analysis, electromagnetic analysis, and acoustic analysis. Both physical and side-channel attacks pose significant risks to systems and devices dependent on embedded systems. These risks manifest as the theft of sensitive information, unauthorized access, or the compromise of the system's functionalities [171]. To counteract such threats, it is imperative to deploy comprehensive security measures. These measures should encompass physical security provisions, such as tamper-resistant packaging and secure boot protocols, alongside cryptographic techniques like encryption and hashing to safeguard sensitive data. In summary, physical and sidechannel attacks exploit or recognize performance characteristics of systems, with invasive attacks involving physical interference and non-invasive attacks exploiting performance indirectly. Implementing a robust security framework, which includes physical safeguards, cryptographic protections, and regular security audits to uncover and rectify potential vulnerabilities, is crucial in preventing these types of attacks [32]. A depiction of the side-channel attack process can be found in Figure 2.2.

#### **Side Channel Attacks**

Figure 2.2 Diagram of side channel attacks [8].

Invasive attack: Invasive attacks necessitate physical access to the device or system and involve directly tampering with the device to interfere with, operate, and observe its internal components. These attacks can have goals such as reading out the implementation of IP cores or extracting secret information, manipulating or damaging data or circuits, or accessing sensitive information [8]. Invasive attacks often result in irreversible modifications to the physical properties of the chip, employing standard reverse engineering techniques like optical or scanning electron microscopy (SEM). Certain invasive attacks may require special equipment and extensive time, potentially weeks, in specialized laboratories, with micro-probing and design reverse engineering being notable examples [32]. Despite their complexity and the high level of resources required, making them less common, the threat of invasive attacks remains significant. To counteract these threats, implementing physical security measures like tamper-resistant packaging and secure boot protocols is crucial. Regular security audits play a vital role in identifying and mitigating vulnerabilities that could be exploited via invasive attacks.

Non-invasive attacks: Non-invasive attacks, also known as side-channel attacks, differ fundamentally in that they do not necessitate physically opening the device or system. These attacks exploit the system's emissions or operational behaviors, such as power consumption, electromagnetic emissions, timing information, or induced faults, during cryptographic processes to extract sensitive information. Non-invasive attacks, including power analysis, electromagnetic (EM) analysis, time analysis, and fault injection attacks, require an initial investment of time or creativity but are generally more affordable and scalable than their invasive counterparts [8]. To safeguard against non-invasive attacks, it's imperative to deploy strong cryptographic protocols and countermeasures like masking or blinding techniques, which obfuscate the information attackers seek. Physical security measures, including tamper-resistant packaging and secure boot protocols, further fortify defences against unauthorized access [8-10]. While invasive attacks involve direct physical tampering and are less common due to their complexity and resource requirements, noninvasive attacks pose a scalable and relatively low-cost threat by exploiting indirect system properties. Addressing both requires a comprehensive security strategy encompassing strong cryptographic defences, physical security measures, and ongoing vigilance through security audits.

Figure 2.3 Attacks on embedded systems.

It is important to understand that side-channel attacks are designed to exploit weaknesses in the design and implementation of a system. These attacks typically involve monitoring the physical properties of a system while cryptographic operations are being performed, in order to uncover sensitive information. Several types of side-channel attacks can be used to compromise a system. One such attack is a power analysis attack, which involves monitoring the power consumption of a device during cryptographic operations to extract secret keys or other sensitive information. Another type of attack is a time analysis attack, which involves measuring the time it takes for a device to perform cryptographic operations to extract sensitive information [9]. EM analysis attacks are another common type of side-channel attack. These attacks involve monitoring the electromagnetic radiation emitted by a device during cryptographic operations to extract sensitive information. Fault induction attacks are also used to exploit weaknesses in the design of a system. These attacks involve inducing faults or errors in a device to extract sensitive information. Overall, side-channel attacks are a significant threat to the security of cryptographic systems. They can be difficult to detect and can be carried out using relatively simple equipment, making them accessible to attackers with limited resources. As such, it is important to understand the different types of side-channel attacks and to take steps to mitigate the risk of their exploitation [10].

## 2.3.4.1 Different Types of Physical and Side-Channel Attacks

### 2.3.4.1.1 Power Analysis Attacks

Power analysis attacks refer to the analysis of the power consumption during the system's data analysis [11]. In electronic systems and devices, the instantaneous power is dependent on the information and data that is being processed in the system as well as the process performed by the system. Therefore, by analysing the power consumption of the system when it operates encryption or decryption, the key can be deduced [12].

Power Analysis attacks can be classified into three categories, Simple power analysis, Differential Power Analysis, and Correlation power analysis attacks [13].

## 2.3.4.1.2 Simple Power Analysis (SPA)

Simple power analysis (SPA) is a technique of side-channel attacks that monitors the power consumption in real time during the operation of cryptographic algorithms and processes in progress. Being possible to break the Advanced Encryption Standard (AES) in a few minutes, power analysis attacks have become a serious security issue for cryptographic devices such as smart cards. These attacks analyse the chip's present power consumption during a period of time. As it can be said each operation will have different power consumption profiles, that establish what type of function has been performed. For instance, there is a distinguishing multiplication function from an addition function based on the usage of the power between multiplications compared to addition. In addition, from the reading of the data from memory, the ratio of 1's vs. 0's will show in the power profile in this attack, attackers directly analyse and evaluate the power consumption. Of course, the power consumption during each operation is different and it also depends on the construction of the microprocessor that performs the execution [13]. The SPA attack is relatively simple to carry out and can be performed using inexpensive equipment. By analysing the power consumption of a device during cryptographic operations, an attacker can observe patterns that can be used to deduce sensitive information about the cryptographic algorithm being used. To prevent SPA attacks, countermeasures such as power analysis-resistant designs and algorithms can be employed. One approach is to use masking techniques to add random values to the data being processed, making it more difficult for attackers to extract sensitive information from the power consumption patterns. Another approach is to use power analysis-resistant algorithms that are designed to minimize the power consumption variations

during cryptographic operations [14]. Overall, Simple Power Analysis attacks are a significant threat to the security of cryptographic systems. However, by understanding the techniques used in these attacks and implementing appropriate countermeasures, it is possible to mitigate the risk of their exploitation [13].

## 2.3.4.1.3 Differential Power Analysis (DPA)

Differential Power Analysis (DPA) attacks are a statistical technique that can exploit the power consumption to identify data information to extract the secret keys while the cryptographic algorithm is running on the system. DPA attacks use the weakness that correlates between the electricity that is used in a chip of a smart card and the encryption key it contains. In this attack, the attacker analysis the power consumption information of the system during the cryptographic algorithm running on the device to break the key differential power attack runs in a different section of the chip and then applies statistical analysis to avoid the countermeasures, like added noise, which can be applied to hide each bit. Measuring the power that has been used can determine what kind of computational operations are carried out by a device. Therefore, this analysis will disclose a few bits of the crypto at each time; this process is continually carried out till eventually, the entire key is produced. Successful DPA attacks have been shown on a wide range of encryption algorithms. This attack is stronger than a simple power attack [13]. Furthermore, DPA attacks are more sophisticated than SPA attacks and require more advanced equipment and techniques. In a DPA attack, an attacker first captures power consumption traces of a device performing cryptographic operations with known inputs. The attacker then analyses these traces to extract information about the secret key being used in the cryptographic algorithm. To prevent DPA attacks, countermeasures such as masking and blinding can be employed. Masking involves adding random values to the data being processed, making it more difficult for attackers to extract sensitive information from the power consumption traces. Blinding involves modifying the cryptographic algorithm to prevent attackers from deducing sensitive information about the secret key. Overall, DPA attacks are a significant threat to the security of cryptographic systems. They require more advanced techniques than Simple Power Analysis attacks, but they can still be carried out using relatively simple equipment. By implementing appropriate countermeasures, it is possible to mitigate the risk of DPA attacks and protect sensitive information [15].

It's important to note that DPA is a sophisticated and non-invasive attack that requires specialized equipment and expertise. To defend against DPA, countermeasures such as masking, shuffling, or other secure hardware and software implementations are employed [11].

### 2.3.4.1.4 Correlation Power Analysis (CPA)

Correlation power analysis (CPA) attack is a new method of the DPA. In these attacks, the attackers make a model of power consumption during the analysis step. CPA attack is a powerful analysis attack that is capable of breaking a cipher by using a combination of the power consumption of the device and the hamming weight of the key-dependent values of the algorithm. These attacks are statistical attacks and use the Pearson correlation modulus to correlate data or information [14]. In a CPA attack, an attacker first captures power consumption traces of a device performing cryptographic operations with known inputs. The attacker then uses statistical techniques to analyse the correlation between the power consumption and the data being processed. By analysing these correlations, an attacker can deduce sensitive information about the secret key being used in the cryptographic algorithm [16]. To prevent CPA attacks, countermeasures such as masking and blinding can be employed. Masking involves adding random values to the data being processed, making it more difficult for attackers to extract sensitive information from the power consumption traces. Blinding involves modifying the cryptographic algorithm to prevent attackers from deducing sensitive information about the secret key. Overall, CPA attacks are a significant threat to the security of cryptographic systems. They require some level of expertise and equipment, but they can still be carried out using relatively simple equipment. By implementing appropriate countermeasures, it is possible to mitigate the risk of CPA attacks and protect sensitive information [13]. A Brief Comparison of CPA attacks with other attack algorithms such as DPA attacks shows that they have a wide range of advantages for example they require a smaller number of power traces [15].

There are different steps to a CPA attack and these steps can be written as follows:

As the first step of the attack, the power traces can be used to gather the information of the plain text. For the next steps, the attackers assume a model of power consumption. Now the attackers can guess a key. After the guesses, the key can be used to calculate the intermediate value using the found guess key. In addition, during the cryptographic operations, the intermediate value will be generated. From this section variable data values and part of the key must be selected. This is

known as the selection function. For example, in the below equation, 'I' indicates the intermediate value 'd' indicates the plain text or the ciphertext and 'k' is a part of the key known as the subkey [15-16].

$$I = F(d, k) \tag{2.1}$$

Then power measurements should be done during the cryptographic operation running on the device [15]. CPA, like DPA, requires specialized equipment and expertise to conduct successfully. To defend against CPA, countermeasures such as noise addition, power shaping, or using hardware components with built-in resistance to side-channel attacks can be implemented. Regular security audits and evaluation of the embedded systems can also help identify and address potential vulnerabilities [13].

### 2.3.4.1.5 Countermeasures against Power Analysis Attacks

Countermeasures are implemented to prevent or make power analysis attacks more difficult to execute. However, it is important to note that no countermeasure can guarantee a hundred percent effectiveness against all types of power analysis attacks.

The effectiveness of a countermeasure can be measured by the level of difficulty an attacker would face in executing a successful power analysis attack. If the time and cost required to execute such an attack are significant, then the countermeasure can be considered effective. Effective countermeasures against power analysis attacks include techniques such as masking and blinding, which add random values to the data being processed and modify the cryptographic algorithm, respectively. These techniques make it more difficult for attackers to extract sensitive information from the power consumption traces. Other countermeasures include using power analysis-resistant designs and algorithms, reducing the power consumption variations during cryptographic operations, and physically isolating the cryptographic device from external influences. Therefore, while no countermeasure can guarantee absolute protection against power analysis attacks, implementing appropriate countermeasures can significantly increase the level of difficulty for attackers and reduce the risk of successful attacks [34].

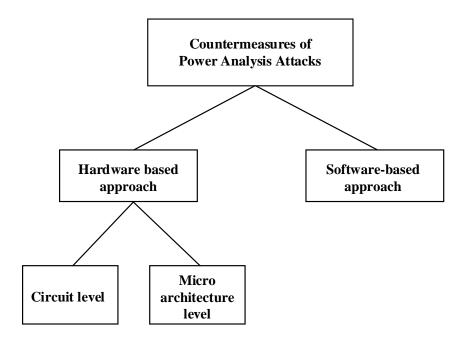

Figure 2.4 Classification of countermeasures against power analysis attacks.

As Figure 2.4 has been shown, the countermeasures against the power analysis attack are classified into two categories: hardware-based and software-based. Hardware-based countermeasures, as the name implies, involve adding new components or modifying existing components of a cryptosystem in order to reduce the leakage of sensitive information and data, such as power consumption. One example of a hardware-based countermeasure is the use of tamper-resistant hardware, which is designed to make it more difficult for attackers to extract sensitive information from a device. Tamper-resistant hardware typically includes features such as physical shielding, hard-to-read memory, and secure boot mechanisms, all of which help to prevent attackers from tampering with or extracting data from the device. Another example of a hardware-based countermeasure is the use of differential power analysis-resistant hardware, which is designed to minimize power consumption variations during cryptographic operations, making it more difficult for attackers to extract sensitive information from power consumption traces [34]. In addition, hardware-based countermeasures can also include the use of specialized processors, such as Field Programmable Gate Arrays (FPGAs) or Application-Specific Integrated Circuits (ASICs), which are designed to perform cryptographic operations more efficiently and securely than traditional processors. Overall, hardware-based countermeasures can be effective in reducing the risk of power analysis attacks. However, they can also be expensive to implement and may not be feasible for all types of devices. It is important to carefully evaluate the costs and benefits of hardware-

based countermeasures before implementing them in a cryptosystem [35]. Hardware countermeasures can be categorized into two broad circuit-level and microarchitecture-level countermeasures. Circuit-level countermeasures include adding additional components to the circuits or making some changes to the circuits at an immense level. For instance, adding a source of noise or connecting a power line filter to the cryptographic device. Microarchitecture-level countermeasures include adding additional components or making some changes at the logic gate level. To illustrate the point, consider that to make a different power consumption, attackers add extra transistors to a CMOS gate [34-36].

Software-based countermeasures, as the name suggests, involve making modifications to the program or data code implemented on the microcontrollers of cryptographic systems. These modifications are intended to prevent attackers from extracting sensitive information from power consumption traces. One example of a software-based countermeasure is the use of random instruction insertion, where incorrect instructions are randomly inserted into the code being executed by the microcontroller. This makes it more difficult for attackers to determine which instructions are related to the cryptographic operation and which are not. Another example is the use of instruction permutation, where the order of instructions is randomized to make it more difficult for attackers to analyse the power consumption traces and extract sensitive information. Other software-based countermeasures include algorithmic modifications, such as adding noise to the data being processed or modifying the cryptographic algorithm to reduce power consumption variations during cryptographic operations. It is important to note that software-based countermeasures can be less effective than hardware-based countermeasures, as attackers may still be able to extract sensitive information from power consumption traces. However, they are often easier and less expensive to implement and can provide an additional layer of protection against power analysis attacks. Software-based countermeasures can be a valuable addition to a cryptosystem's security measures. It is important to carefully evaluate the effectiveness of any software-based countermeasure before implementing it and to consider the potential impact on system performance and complexity [35].

## 2.3.4.1.6 Security, Performance and Power Analysis of Power Analysis Attacks

Table 2.1 presents a clear depiction of the prevalence of power analysis attacks, indicating that a substantial number of researchers in the field monitor power consumption as a key metric during these attacks. The reason behind this approach lies in the direct correlation between power

consumption and the potential vulnerabilities that can be exploited. By closely observing the fluctuations in power consumption, researchers can effectively identify and analyse the attack patterns, facilitating the development of appropriate countermeasures. The significance of this power-based approach is that it allows researchers to detect subtle variations in power consumption caused by different attack scenarios. By understanding these variations, they can gain valuable insights into the weaknesses of a system and devise targeted defences against potential threats. The advantage of this methodology is that it is applicable across a wide range of devices and architectures, making it a versatile and widely adopted technique in the realm of security analysis. However, it is important to note that implementing countermeasures can sometimes come with trade-offs, particularly in terms of device performance. In certain cases, the integration of robust security measures may lead to a decrease in the overall performance of the devices. This challenge necessitates a careful balance between security and performance, where researchers must explore innovative ways to enhance device security without unduly compromising their efficiency and functionality. To address this concern, researchers often embark on a comprehensive analysis of the trade-offs between security and performance. They explore various mitigation strategies that offer a reasonable compromise between safeguarding against power analysis attacks and maintaining acceptable device performance [13]. This delicate balancing act ensures that the introduced countermeasures not only enhance security but also allow devices to deliver optimal functionality in real-world applications.

Table 2.1 Security, performance and power consideration of power analysis attacks in different research.

| Reference | Attack   | Defence Strategy                       | Performance<br>Consideration | Power<br>Consideration |

|-----------|----------|----------------------------------------|------------------------------|------------------------|

| [11]      | ✓        | Boolean Masking                        | *                            | ×                      |

| [12]      | <b>√</b> | Key-Dependent Control Flow Obfuscation | ×                            | <b>√</b>               |

| [13]      | ✓        | Energy Harvesting Countermeasures      | ✓                            | ✓                      |

| [14]      | <b>√</b> | Logic Locking with Power-Concealing    | ×                            | <b>√</b>               |

|      |          | Transformations                                                |   |          |

|------|----------|----------------------------------------------------------------|---|----------|

| [15] | ✓        | Chaotic Power Supply with Noise Injection                      | * | ✓        |

| [16] | ✓        | Time-Varying Leakage Current Balancing                         | × | <b>√</b> |

| [34] | <b>√</b> | Physical Unclonable Functions (PUFs) for Key Storage           | × | <b>✓</b> |

| [35] | 1        | Generative Adversarial Networks (GANs) for DPA Countermeasures | × | <b>√</b> |

| [36] | <b>√</b> | Privacy-Preserving Statistical Countermeasures                 | × | <b>√</b> |

## 2.3.4.2 Electromagnetic Attacks

Electromagnetic attacks represent a sophisticated category of side-channel attacks that leverage the analysis of electromagnetic radiation emitted by a target system [16]. These attacks have gained prominence due to their non-invasive and passive nature, allowing attackers to exploit the inherent electromagnetic emissions produced during the normal operation of a device without causing any discernible physical harm [17]. This covert characteristic makes EM attacks particularly insidious, as they can compromise sensitive information without triggering immediate suspicion. The fundamental principle underpinning these attacks revolves around the precise measurement and analysis of the electromagnetic radiation emanating from a targeted system. By doing so, attackers can effectively unveil hidden or confidential data processed within the device. Successful execution of an EM attack necessitates an intricate understanding of the intricate layout of the semiconductor chips within the system [16]. Consequently, the measurement of electromagnetic radiation should ideally be conducted within a controlled and isolated environment to ensure the accuracy and reliability of the obtained results [17]. One of the noteworthy advantages of EM attacks is their potential to circumvent traditional security measures that focus on digital