Contention and Reliability-Aware Energy Efficiency Task Mapping on NoC-Based MPSoCs

Lei Mo\*, Member, IEEE, Xinmei Li\*, Student Member, IEEE, Angeliki Kritikakou<sup>†</sup>, Member, IEEE, and Xiaojun Zhai<sup>‡</sup>, Senior Member, IEEE

Abstract—Recently, Network-on-Chip (NoC)-based Multi-Processor System-on-Chips (MPSoCs) have become popular computing platforms for real-time applications due to high communication performance and energy efficiency over traditional bus-based MPSoCs. Due to the nature of network structures, network congestion along with transient faults, can significantly affect communication efficiency and system reliability. Most existing works have rarely focused on the concurrent optimization of network contention, reliability, and energy consumption. Here, we study the problem of contention and reliability-aware task mapping under real-time constraints for dynamic voltage and frequency scaling-enabled NoC. The problem entails optimizing voltage/frequency on cores and links to reduce energy consumption and ensure system reliability, while task mapping and slack time are adopted to alleviate network contention and reduce latency. We aim to minimize computation and communication energy and balance workload. This problem is formulated as a mixed-integer nonlinear programming, and we present an effective linearization scheme that equivalently transforms it into a mixed-integer linear programming to find the optimal solution. To reduce computation time, we propose a three-step heuristic, including task allocation, frequency scaling and edge scheduling, and communication contention management. Finally, we perform extensive simulations to evaluate the proposed method. The results show we can achieve 31.6% and 21.7% energy savings, with 95.5% and 98.6% less contention than the existing methods.

*Index Terms*—Contention-aware, Reliability-aware, Energy Management, Task mapping, NoC.

## I. INTRODUCTION

ITH the increasing demand for high computing performances, e.g., Internet of Things (IoT) [1], big data processes [2], cloud centers [3] and blockchain systems [4], Multi-Processor System-on-Chip (MPSoC) architectures integrate multiple cores into a single platform. The increase in cores leads to many issues and challenges for traditional shared bus-based multicore platforms, such as poor scalability and low communication efficiency due to the limited bus bandwidth [5]. To address the scalability and bandwidth issues, Network-on-Chip (NoC) has been proposed as an interconnection architecture solution with much better scalability, flexibility, parallelism, and communication efficiency, compared to the traditional bus-based multicore platforms [6]. In the NoC-based MPSoCs, e.g., the Ethereal NoC [7], the Versal NoC [8], and the Arteris

NoC [9], the Operating System (OS) can run at each core, responsible for task scheduling, task loading, packet assembly/disassembly, and Direct Memory Access (DMA) management, enabling the platforms to meet multiple constraints.

Furthermore, energy consumption has become an essential issue for the NoC-based MPSoCs as the number of cores increases. To achieve an effective system, appropriate task mapping methods are needed. Most energy-aware task mapping methods in bus-based MPSoCs mainly focus on the energy consumption of computation, e.g., [10]-[12]. To reduce both computation and communication energy consumption, the NoCbased MPSoCs are enhanced with Dynamic Voltage and Frequency Scheduling (DVFS) for cores, routers, and links [13]-[16]. The energy consumption can be reduced by lowering the Voltage/Frequency (V/F) level. However, the decrease in operating V/F levels impacts the transient fault rate on cores, routers, and links, thereby decreasing the system reliability [17]. Therefore, the trade-off between energy consumption and system reliability should be considered during task mapping on NoCbased MPSoCs. Some existing works [18]-[21] have studied the joint design problem of saving energy and enhancing system reliability. For instance, transient faults are considered on links and routers [18], [19] or cores [20], [21]. As transient faults may occur during task execution and communication, it is necessary to consider that they can occur on cores, routers, and links when optimizing task mapping for energy consumption and system reliability on NoC-based platforms.

Due to the nature of the network-based structure, the task mapping strategy on NoC-based platforms may cause network contention among the task data communication over the shared communication resource, i.e., routers and links. If a link is occupied due to the transmission of a message, any other messages requiring the same link will wait until the link becomes available [6], [14]. Network congestion degrades system performance due to the increased transmission delay, thereby affecting the execution time of applications, which is of paramount importance, especially for real-time applications [6]. For the NoC-based platforms, it is necessary to consider communication contention during task mapping. However, most existing works focused on energy and (or) reliability improvement but ignored the influence of communication contention [18], [21]. Other works alleviated the network congestion by introducing fixed slack time into the task scheduling [13]. Note that load imbalance may cause overloading and local network congestion on NoC. Overloading decreases power efficiency and system reliability [22]–[24] since the cores with high computation loads

1

<sup>\*</sup>L. Mo and X. Li are with the School of Automation, Southeast University, 210096 Nanjing, China. E-mails: lmo@seu.edu.cn, xinmeili@seu.edu.cn.

<sup>&</sup>lt;sup>†</sup>A. Kritikakou is with the University of Rennes, INRIA, IRISA, CNRS, 35042 Rennes, France, and also with the Institut Universitaire de France, 75005 Paris, France. E-mail: angeliki.kritikakou@irisa.fr.

<sup>&</sup>lt;sup>‡</sup>X. Zhai is with the School of Computer Science and Electronic Engineering, University of Essex, Colchester CO4 3SQ, U.K., E-mail: xzhai@essex.ac.uk.

stay active most of the time while the remaining cores are idle. To obtain an efficient system, we must simultaneously alleviate network contention, balance workload, and improve energy efficiency and reliability.

To address the above issues, we propose a novel task mapping method to jointly optimize energy efficiency through DVFS while balancing the workload and mitigating the communication contention on the NoC-based platform under real-time and reliability constraints. Therefore, our method is suitable for applications with energy efficiency, reliability, and timeliness requirements, such as autonomous drones [25], and video processing systems [26]. The main contributions of this paper are summarized as follows:

- (1) We holistically model the problem of reducing energy consumption and balancing the workload for NoC-based platforms. DVFS adjusts the V/F levels of cores and links, reducing the total energy consumption under real-time and reliability constraints. Communication contention is considered, where flexible slack time alleviates communication contention, reducing latency.

- (2) Based on the system model, the task mapping problem is formulated as a mixed-integer nonlinear programming (MINLP) problem, with the aim to minimize energy consumption and balance workload under multiple constraints. We apply the linearization method by introducing auxiliary variables and additional constraints and then equivalently transform the original problem into a mixed-integer linear programming (MILP) problem to find the optimal solution.

- (3) Taking advantage of the structure of the task mapping problem, we propose a novel three-step heuristic to find the solutions. First, a dynamic programming-based task allocation heuristic is applied to find the task-to-core decision. Then, the improved feasibility-pump heuristic is used to determine the frequency assignment and the edge scheduling. Finally, we calculate the precise contention slack time and adjust frequencies on cores within the task deadlines to reduce energy.

- (4) We perform simulations on randomly generated task sets and realistic application task sets to evaluate the performance of our method in terms of energy consumption, task reliability, and communication contention. Compared to the state-of-the-art methods [6] and [21], our method achieves 31.6% and 21.7% energy reduction and has 95.5% and 98.6% lower average contention, while balancing workload and satisfying reliability constraints. In addition, compared to the optimal solution, our method has a polynomial computation time, but with only 24.8% lower energy efficiency.

The remainder of this paper is organized as follows. Section II discusses the related work. Section III presents a contention- and reliability-aware task mapping problem. Section IV describes the proposed three-step heuristic. Section V shows the simulation results, and Section VI concludes this paper.

### II. RELATED WORK

To improve system efficiency, such as achieving energy and communication efficiency and reliability, task mapping on NoCbased MPSoCs has gained significant attention in recent years.

TABLE I COMPARISON OF RELATED WORKS

| Ref. | Optimization objectives             | RA | CA | LB |

|------|-------------------------------------|----|----|----|

| [27] | Energy                              | ×  | ×  | ×  |

| [16] | Energy                              | ×  | ×  | ×  |

| [21] | Energy                              |    | ×  | ×  |

| [28] | Task Replication Overhead           |    | ×  | ×  |

| [20] | Energy                              |    | ×  | ×  |

| [29] | Energy + Temperature                |    | ×  | ×  |

| [6]  | Latency                             | ×  |    | ×  |

| [30] | Latency                             | ×  |    | ×  |

| [31] | Makespan                            | ×  |    | ×  |

| [13] | Makespan                            | ×  |    | ×  |

| [32] | Energy + Latency                    | ×  |    | ×  |

| [15] | Energy + Latency                    | ×  |    | ×  |

| [14] | Energy                              | ×  |    | ×  |

| [18] | Energy + Reliability + Latency      |    | ×  | ×  |

| [19] | Energy + Reliability + Latency      |    |    | ×  |

| [22] | Communication Efficiency + Workload | ×  | ×  |    |

| [33] | Energy + Execution Time + Workload  |    | ×  |    |

| [34] | Energy + Makespan + Contention      | ×  |    |    |

| Pro. | Minimize Energy + Balance Workload  |    |    |    |

Table I summarizes some representative works of task mapping on NoC-based MPSoCs, which include Reliability Awareness (RA), Contention Awareness (CA), and Load Balance (LB).

Energy efficiency is essential in NoC-based MPSoCs, especially for battery-powered mobile embedded systems [16]. Several works have studied energy-aware task scheduling on NoC-based MPSoCs [16], [27] to minimize the total energy of computation and communication under real-time constraints. However, using low operating frequency to execute tasks may impact task reliability, increasing the appearance of transient faults. To address this issue, some approaches introduce reliability constraints into energy-aware task mapping problem [20], [21]. For transient faults occurring on cores, a fixed faulttolerant policy is applied [21], where tasks are duplicated, and frequencies are adjusted simultaneously. To mitigate the transient faults while improving real-time response, a faulttolerant method selects from several policies, i.e., checkpointing, task replication, and checkpointing with task replication techniques [20]. A fault-tolerant mechanism based on the backup copy that simultaneously optimizes temperature and energy consumption is proposed in [29]. The primary task and backup copy are executed on the primary and backup cores, respectively, and the backup cores are used only when failures exist in the primary cores. However, task replication introduces replicas, which increases computation and communication costs. To minimize task replicas and latency, [28] jointly addresses transient faults of cores, links, and routers on NoCs.

Communication latency is another critical issue, as it affects the execution time of mapped applications, especially for real-time applications [6]. To minimize the communication latency, approaches focus on the link contention between data transfers over NoC [6], [30], [31]. In [6], [30], contention metrics are introduced to identify the links of NoC with high loads, which are prone to suffer congestion. The latency can be minimized by bypassing the congested links. The communications with potential contentions are prioritized, and priorities are used to reduce the makespan [31]. However, the above methods only consider optimizing communication efficiency, whereas energy

efficiency and reliability are not considered.

Considering network contention, several works [13]–[15], [32], [34] jointly optimize energy and latency. Few works also take into account reliability [18], [19]. Considering energy- and contention-aware task mapping on NoCs, the communication latency is optimized in [13], [32] by adding a fixed latency time into task scheduling, where the fixed latency time is calculated by the worst congestion estimation to alleviate the impact caused by link congestion. Energy consumption can be further reduced through task mapping and DVFS. However, introducing a fixed latency time may postpone task completion time. Therefore, optimizing task assignment and operation frequency can help in meeting task deadlines. Communications with contentions are prioritized to minimize energy consumption [14], [15], [31]. Compared to [14] that only considers DVFS, [15] integrates DVFS and DPM (Dynamic Power Management) techniques together to reduce further energy consumption. The optimization of the communication energy, reliability, and latency on NoCs is proposed in [18] by assigning the tasks onto a redundant core to avoid faulty links. Remapping and wait mechanisms are applied to solve the faults on cores, links, and routers while introducing fixed waiting time due to congestion into the scheduling [19]. However, the methods mentioned above only consider communication energy, more overhead is introduced for task remapping, they require redundant NoC hardware, and they omit the workload balance.

Regarding workload balance, it is optimized to improve the system [22], [33], [34]. For instance, a trade-off task mapping method balances workload and communication efficiency to reduce task execution time in [22]. Considering faults on routers, task reliability is tackled simultaneously considering energy consumption, execution time, and load balancing [33], but without network contention. An optimization method considering energy, makespan, and contention is proposed to avoid spatial and temporal contentions in [34]. However, the frequency adjustment and real-time constraints are not taken into account. Compared to the state-of-the-art methods in Table I, our work minimizes energy consumption and balances workload under real-time and reliability constraints while alleviating the network contention on the NoC-based platform.

# III. SYSTEM MODEL AND PROBLEM FORMULATION

### A. System Model

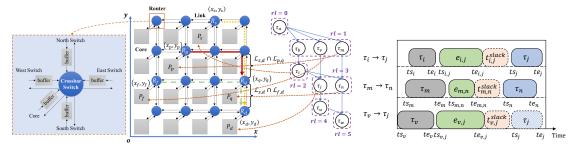

1) NoC Model: The target platform is a 2D mesh NoC-based homogeneous MPSoCs, as it is widely used in current NoC architecture [13], [14], [27]. The platform has a set  $\mathcal{P} \triangleq \{P_1,\ldots,P_M\}$  of M cores, and a set  $\mathcal{R} \triangleq \{R_1,\ldots,R_M\}$  of M corresponding routers. For a 2D mesh NoC topology, as shown in Fig. 1(a), each router  $R_s$  has five I/O ports, where four ports are linked to the neighboring routers, while one is associated with the corresponding core  $P_s$  [13]. In addition, each port has a link and a buffer to transmit and store the data, respectively. All the cores and links in the NoC platform are DVFS-enabled. Each core can operate on a set  $\{(v_{p,1},f_{p,1}),\ldots,(v_{p,N_p},f_{p,N_p})\}$  of  $N_p$  discrete V/F levels, where  $(v_{p,k},f_{p,k})$  denotes the  $k^{th}$  V/F level of the core  $(1 \leq k \leq N_p)$ . Similarly, each link can operate at a set  $\{(v_{l,1},f_{l,1}),\ldots,(v_{l,N_l},f_{l,N_l})\}$  of  $N_l$  discrete

V/F levels, and  $(v_{l,g}, f_{l,g})$  denotes the  $g^{th}$  V/F level of the link  $(1 \leq g \leq N_l)$ . We adopt the deterministic XY routing, a popular routing method on 2D mesh NoC [13], [14], [27]. The routing set of physical links between cores  $P_s$  and  $P_d$  is  $\mathcal{L}_{s,d} \triangleq \{l_{s,i},\ldots,l_{j,d}\}$ , where  $l_{s,i}$  (or  $l_{j,d}$ ) denotes the physical link between cores  $P_s$  and  $P_i$  (or cores  $P_j$  and  $P_d$ ), and each link  $l_{s,d}$  is full duplex with a bandwidth  $l_{\omega}$ . The distance between  $l_s$  and  $l_s$  represents the number of links in the set  $l_s$ , and it can be measured by the Manhattan distance  $l_s$ ,  $l_s$ , and  $l_s$ ,  $l_s$ , and  $l_s$ ,  $l_s$ , where  $l_s$ ,  $l_s$ , and  $l_s$ ,  $l_s$ , are the coordinates of cores  $l_s$ , and  $l_s$ ,

2) Task Model: A real-time application with N dependent tasks is modeled as a Directed Acyclic Graph (DAG) with 6-tuple elements  $\{\mathcal{T}, \mathcal{E}, \mathcal{S}, \mathcal{W}, \mathcal{D}, H\}$ .  $\mathcal{T} \triangleq \{\tau_1, \dots, \tau_N\}$  is a real-time task set with N tasks.  $\mathcal{E}$  denotes the set of edges, where each edge  $e_{i,j}$  represents the dependency between tasks  $\tau_i$  and  $\tau_j$ . Each edge has a weight  $s_{i,j} \in \mathcal{S}$ , representing the size of communication data between  $\tau_i$  and  $\tau_j$ . Each task  $\tau_i$  has  $\omega_i \in \mathcal{W}$  cycles, measured by Worst-Case Execution Cycles (WCEC). Task  $\tau_i$  is released at time 0 and has an individual deadline  $D_i \in \mathcal{D}$ . H is the scheduling horizon, which is also the period of task  $\tau_i$ . Due to the dependency, each task  $\tau_i$  cannot start execution until all its predecessors' input data has arrived. At the same time, the output data is concurrently available for transmission to all its successors only when it completes execution.

We consider the transmission time over links for task data communication since the extra overheads (e.g., data copy between buffers and inter-router delay) are negligible compared with the transmission time [13]. Besides, we consider that the transmission time is increased with the routing distance. For the edge  $e_{i,j}$ , if the data with the size  $s_{i,j}$  is transmitted from  $\tau_i$  to  $\tau_j$  by one unit link, the link transmission time with the V/F level  $(v_{l,q}, f_{l,q})$  is calculated as

$$t_{i,j,g}^{UL} = s_{i,j}/(b_{\omega}f_{l,g}), \ \forall e_{i,j} \in \mathcal{E}, \ 1 \le g \le N_l.$$

(1)

If the routing distance is more than one unit, e.g., tasks  $\tau_i$  and  $\tau_j$  are assigned to different cores  $P_s$  and  $P_d$ , and the routing distance associated with the edge  $e_{i,j}$  is  $h_{s,d}$ , the transmission time with the V/F level  $(v_{l,g},f_{l,g})$  is computed as  $t_{i,j,g}^L = h_{s,d}t_{i,j,g}^{UL}$ . If two tasks are assigned to the same core, the communication cost between them is assumed to be zero.

3) Energy Model: Since each core and link can operate on different V/F levels, switching brings extra overhead to energy consumption and execution time. Compared with the energy and time required for task execution and data communication, the switching overhead is very small, especially when the switching rate is low. Hence, we omit the overhead of frequency switching [14], [16], [27]. We consider the power dissipation by computation and communication in the power model. Given the V/F level  $(v_{p,k}, f_{p,k})$ , the computation power  $P_k^{comp}$  dissipated in executing tasks is computed as follows [27]:

$$P_{k}^{comp} = \underbrace{C_{eff}v_{p,k}^{2}f_{p,k}}_{\text{dynamic power}} + \underbrace{L_{g}\left(v_{p,k}I_{sub} + |v_{bs}|I_{j}\right)}_{\text{static power}}, \quad (2)$$

where  $C_{eff}$ ,  $L_g$ ,  $I_{sub}$ ,  $v_{bs}$ , and  $I_j$  denotes the effective switching capacitance, the number of devices in the circuit, the subthreshold leakage current, the body bias voltage, and the reverse

- (a) Task mapping of Gauss elimination on a  $4 \times 4$  NoC with XY routing.

- (b) Task execution and communication time.

Fig. 1. An example of task mapping with communication contention.

bias junction current, respectively. Besides the V/F level, the operating temperature also influences the static power. In this paper, we did not consider temperature, as it will introduce another dimension of variables into the task mapping problem, making it more difficult to solve. Instead, we mainly focus on optimizing energy efficiency, reliability, and communication contention, similar to the existing works [16], [20], [21].

The following link power model is adopted from [27]:

$$P_g^{link} = s_a C_{rep} v_{l,g}^2 f_{l,g} + L_g \left( v_{l,g} K_3 e^{K_4 v_{l,g}} e^{K_5 v_{bs}} + |v_{bs}| I_j \right),$$

(3)

where  $s_a$  is the average switching activity,  $C_{rep}$  is capacity load of a repeater, and  $K_3$ ,  $K_4$  and  $K_5$  are hardware parameters.

Note that the routers and the links on NoC mainly consume communication energy. The communication energy for edge  $e_{i,j}$  with the data size  $s_{i,j}$  from core  $P_s$  to  $P_d$ , if it is operated at the V/F level  $(v_{l,g}, f_{l,g})$  [14], [27], is given by:

$$E_g^{comm} = s_{i,j} \left[ (h_{s,d} + 1) E_{Rbit} + h_{s,d} E_{Lbit,g} \right],$$

(4)

where  $E_{Rbit}$  is the energy consumption of transmitting a bit data on a router, and  $E_{Lbit,g} = P_g^{link}/b_\omega f_{l,g}$  is the energy consumed by transmitting a bit data over a link with the frequency  $f_{l,g}$ . Since  $h_{s,d}$  is the number of the links that a bit data passes during the communication,  $h_{s,d}+1$  is the number of routers that a bit data passes. On this basis,  $(h_{s,d}+1)E_{Rbit}$  is the energy consumption of transmitting a bit data for routes, while  $h_{s,d}E_{Lbit,g}$  is the energy consumption of transmitting a bit data with the V/F  $(v_{l,g},f_{l,g})$  on links.

4) Communication Contention Model: In NoC, any physical link can only transmit one message at the same time; otherwise, communication contention occurs, leading to data transmission blocking and system performance degradation. The existence of communication contention should satisfy the time and space constraints. For instance, we assume that tasks  $\tau_i$ ,  $\tau_j$ ,  $\tau_m$ ,  $\tau_n$ , and  $\tau_v$  are assigned to cores  $P_s$ ,  $P_d$ ,  $P_p$ ,  $P_q$ , and  $P_f$ , respectively. For these dependent tasks, the routing sets of the communication for the edges  $e_{i,j}$ ,  $e_{m,n}$ , and  $e_{v,j}$  are  $\mathcal{L}_{s,d}$ ,  $\mathcal{L}_{p,q}$ , and  $\mathcal{L}_{f,d}$ , as shown in Fig. 1(a).

The communication contention in time is defined as the overlap of communication time for different edges, such as edges  $e_{i,j}$  and  $e_{m,n}$  in Fig. 1(b). If there is a communication time overlapping among  $e_{i,j}$  and  $e_{m,n}$ , the contention constraints in time can be expressed as  $ts_{i,j} < te_{m,n}$  and  $ts_{m,n} < te_{i,j}$ , where  $ts_{i,j}$  and  $ts_{m,n}$  ( $te_{i,j}$  and  $te_{m,n}$ ) denote the start time (end time) of data transmission for edge  $e_{i,j}$  and  $e_{m,n}$ .

To indicate the sequence between  $e_{i,j}$  and  $e_{m,n}$ , we introduce a binary variable  $\eta_{i,j,m,n}$ , where  $\eta_{i,j,m,n} = 1$  denotes that edge

$e_{i,j}$  begins communication before  $e_{m,n}$  completes, otherwise,  $\eta_{i,j,m,n}=0$ . Note that the value of  $\eta_{i,j,m,n}$  is influenced by the start time and the end time of the edges  $e_{i,j}$  and  $e_{m,n}$ , the relationship between them can be represented as

$$(te_{m,n} - ts_{i,j})/Z \le \eta_{i,j,m,n} \le (te_{m,n} - ts_{i,j})/Z + 1, \quad (5)$$

$$(te_{i,j} - ts_{m,n})/Z \le \eta_{m,n,i,j} \le (te_{i,j} - ts_{m,n})/Z + 1, \quad (6)$$

$$e_{i,j} \ne e_{m,n} \in \mathcal{E}, \quad \eta_{i,j,m,n}, \eta_{m,n,i,j} \in \{0,1\},$$

where Z is a large positive integer. When  $ts_{i,j} < te_{m,n}$  holds, (5) is relaxed to  $\eta_{i,j,m,n} = 1$ . Similarly, when  $ts_{m,n} < te_{i,j}$  holds, (6) can be transformed into  $\eta_{m,n,i,j} = 1$ . As the example shown in Fig. 1(b), since there is a time overlap between the edges  $e_{i,j}$  and  $e_{m,n}$ , we have  $\eta_{i,j,m,n} = \eta_{m,n,i,j} = 1$ .

The communication contention in space is defined that the routing sets of the edges have at least one shared link, e.g., in Fig. 1(a), for the edges  $e_{i,j}$  and  $e_{m,n}$ , we have  $\mathcal{L}_{s,d} \cap \mathcal{L}_{p,q} \neq \emptyset$ , where  $\mathcal{L}_{s,d} \cap \mathcal{L}_{p,q}$  denotes the common links between the routing sets of the edges  $e_{i,j}$  and  $e_{m,n}$ . Hence, the communication contention occurs between the edges  $e_{i,j}$  and  $e_{m,n}$ .

To alleviate the contention, we add flexible slack time into the communication process to ensure that the congested data can be transmitted sequentially. The slack time with a fixed value will generate additional idle time on cores, increasing energy consumption [13], [32]. In this paper, we set slack time as an adaptive value, which depends on the communication cost of overlapping links.

The slack time  $t_{i,j}^{slack}$  and  $t_{m,n}^{slack}$  for the edges  $e_{i,j}$  and  $e_{m,n}$  can be given by:

$$e_{i,j} \neq e_{m,n} \in \mathcal{E}, \ P_s \neq P_d, P_p \neq P_q \in \mathcal{P}, \ t_{i,j}^{slack}, t_{m,n}^{slack} \geq 0,$$

$$t_{i,j}^{slack}, t_{m,n}^{slack} \geq |\mathcal{L}_{s,d} \cap \mathcal{L}_{p,q}| \cdot \max \left\{ \overline{t_{i,j}^{UL}}, \overline{t_{m,n}^{UL}} \right\} -$$

$$Z(6 - x_{i,s} - x_{j,d} - x_{m,p} - x_{n,q} - \eta_{i,j,m,n} - \eta_{m,n,i,j}),$$

(7)

where  $|\mathcal{L}_{s,d} \cap \mathcal{L}_{p,q}|$  denotes the number of overlapping links between the edges  $e_{i,j}$  and  $e_{m,n}$ ; binary variable  $x_{i,s}=1$  denotes task  $\tau_i$  is assigned to core  $P_s$ , otherwise,  $x_{i,s}=0$ ; binary variable  $c_{i,j,g}^L=1$  denotes the message for edge  $e_{i,j}$  is transmitted with  $(v_{l,g},f_{l,g})$ , otherwise,  $c_{i,j,g}^L=0$ ;  $\overline{t_{i,j,g}^{UL}}=\sum_{g\in\mathcal{N}_l}c_{i,j,g}^Lt_{i,j,g}^{UL}$  is the transmission time on one unit link for the edge  $e_{i,j}$ . Similarly, for the edge  $e_{m,n}$  we have  $\overline{t_{m,n}^{UL}}=\sum_{g\in\mathcal{N}_l}c_{m,n,g}^Lt_{m,n,g}^{UL}$ .

As the example shown in Fig. 1, we have  $x_{i,s} = x_{j,d} = x_{m,p} = x_{n,q} = x_{v,f} = 1$ . When contention constraints in time and space are satisfied, i.e.,  $\eta_{i,j,m,n} = \eta_{m,n,i,j} = 1$

and  $\mathcal{L}_{s,d} \cap \mathcal{L}_{p,q} \neq \emptyset$ , the communication contention happens between the edges  $e_{i,j}$  and  $e_{m,n}$ . Therefore, (7) is relaxed to

$$t_{i,j}^{slack}, t_{m,n}^{slack} \ge |\mathcal{L}_{s,d} \cap \mathcal{L}_{p,q}| \times \max\left\{\overline{t_{i,j}^{UL}}, \overline{t_{m,n}^{UL}}\right\}.$$

(8)

Note that the edges can operate at different V/F levels, and communication contention could happen over multiple edges simultaneously. For edges  $e_{i,j}$  and  $e_{m,n}$ , the maximum communication time on overlapping links is  $|\mathcal{L}_{s,d} \cap \mathcal{L}_{p,q}| \cdot \max\{\overline{t_{i,j}^{UL}}, \overline{t_{m,n}^{UL}}\}$ . If there is no communication contention, i.e., contention constraints regarding time and space are not satisfied, since  $\eta_{i,j,m,n} + \eta_{m,n,i,j} \leq 1$  and  $\mathcal{L}_{s,d} \cap \mathcal{L}_{p,q} = \emptyset$ , we have  $-Z(6-x_{i,s}-x_{j,d}-x_{m,p}-x_{m,q}-\eta_{i,j,m,n}-\eta_{m,n,i,j}) \ll 0$  and  $|\mathcal{L}_{s,d} \cap \mathcal{L}_{p,q}| = 0$ , and thus, (7) is relaxed to  $t_{i,j}^{slack}, t_{m,n}^{slack} \geq 0$ , which can be ignored since the lower bound of continuous variables  $t_{i,j}^{slack}$  and  $t_{m,n}^{slack}$  is 0. Similarly, for the contention between  $e_{i,j}$  and  $e_{v,j}$ , we can get

$$t_{i,j}^{slack}, t_{v,j}^{slack} \ge |\mathcal{L}_{s,d} \cap \mathcal{L}_{f,d}| \times \max\left\{\overline{t_{i,j}^{UL}}, \overline{t_{v,j}^{UL}}\right\}.$$

(9)

When the contention happens over multiple edges concurrently, e.g.,  $e_{i,j}$ ,  $e_{m,n}$ , and  $e_{v,j}$  in Fig. 1(b), the lower bound of slack time  $t_{i,j}^{slack}$  should be updated according to (8) and (9), since  $t_{i,j}^{slack}$  is influenced by  $t_{m,n}^{slack}$  and  $t_{v,j}^{slack}$  at the same time. 5) Fault-tolerant Model: During the application execution

5) Fault-tolerant Model: During the application execution process, several faults can affect the system reliability, e.g., transient faults, intermittent faults, and permanent faults. We mainly focus on transient faults on cores, routers, and links since transient faults have higher rates than intermittent and permanent faults [29]. In addition, a fault on a router may affect the links connected to this router. In the worst case, a fault in any part of a router can be treated as a fault occurring in all the links related to the faulty router [18]. Therefore, we assume that the faults on routers are included in the faults over the links.

We consider that the average rate caused by transient faults is followed by the Poisson distribution [17], [35], [36]. Besides, the fault rate is affected by the voltage the system is run at [17]. Hence, the fault rate with a scaled frequency f can be modeled as  $\lambda(f) = \lambda_0 \times 10^{\frac{d(f_{\max}-f)}{f_{\max}-f_{\min}}}$ , where  $\lambda_0$  is the average fault rate at  $f_{\max}$ , and d is a positive constant, representing the sensitivity of faults caused by transient faults to DVFS. Thus, the probability of success for a task on a hardware component with fault rate  $\lambda(f)$  within the time interval t is  $e^{-\lambda(f)\times t}$ .

Considering the homogeneity of the NoC platform, we set the fault rates of cores and links as  $\lambda_P(f)$  and  $\lambda_L(f)$ , respectively. The probability of success for task  $\tau_i$  with the frequency  $f_{p,k}$  on core  $P_s$  can be calculated as  $r_{i,k}^P = e^{-\lambda_P(f_{p,k}) \times t_{i,k}^P}$ , where  $t_{i,k}^P = \frac{\omega_i}{f_{p,k}}$  denotes the execution time of task  $\tau_i$  with V/F level  $(v_{p,k},f_{p,k})$ . Similarly, the probability of successful transmission over one unit link for edge  $e_{i,j}$  with the frequency  $f_{l,g}$  can be given by  $r_{i,j,g}^{UL} = e^{-\lambda_L(f_{l,g}) \times t_{i,j,g}^{UL}}$ . In Fig. 1(a), when tasks  $\tau_i$  and  $\tau_j$  are assigned to cores  $P_s$  and  $P_d$ , respectively, the probability of success for edge  $e_{i,j}$  along route  $\mathcal{L}_{s,d}$  with the frequency  $f_{l,g}$  is  $r_{i,j,g}^L = \sum_{s \in \mathcal{M}} \sum_{d \in \mathcal{M}} x_{i,s} x_{j,d} (r_{i,j,g}^{UL})^{h_{s,d}}$ , where  $(r_{i,j,g}^{UL})^{h_{s,d}}$  represents the reliability probability of route  $\mathcal{L}_{s,d}$  containing  $h_{s,d}$  links. On this basis, the joint reliability probability of task  $\tau_j$  can be calculated as

$$R_{j} = r_{j,k}^{P} \times r_{i,j,g}^{L} \times r_{v,j,g}^{L} = r_{j,k}^{P} \prod_{e_{u,j} \in \mathcal{E}} r_{u,j,g}^{L},$$

(10)

where  $\prod_{e_{u,j} \in \mathcal{E}} r_{u,j,g}^L$  denotes the probability of successful transmission between task  $\tau_j$  and its predecessors with the frequency  $f_{l,g}$ . If a task does not have any predecessors, e.g., task  $\tau_a$  in Fig. 1(a), we consider only the faults on cores, and thus, the reliability probability of task  $\tau_a$  is  $R_a = r_{a,k}^P$ . To maintain the desired system reliability, each task  $\tau_j$  must satisfy its reliability constraints [21], which means the task reliability  $R_j$  is greater than the reliability threshold  $R_{th}$ .

### B. Problem Formulation

This section presents the Mixed-Integer Nonlinear Programming (MINLP) formulation of the contention- and reliability-aware mapping problem. Our goal is to schedule and route each task such that real-time and reliability constraints are satisfied and the system performance (i.e., communication efficiency, energy consumption, and core utilization) is improved. Therefore, we must determine 1) task allocation, 2) frequency assignment, 3) edge scheduling, and 4) communication contention management. To formulate the task mapping problem, we introduce a set of binary and continuous variables, as summarized in Table II. For the sake of paper presentation, let  $\mathcal{N} \triangleq \{1, \dots, N_l\}$ ,  $\mathcal{M} \triangleq \{1, \dots, N_l\}$ . The constraint descriptions are as follows:

1) Task Allocation Constraints: The task allocation variable  $x_{i,s}$  is bounded by

$$\sum_{s \in \mathcal{M}} x_{i,s} = 1, \ \forall i \in \mathcal{N}, \tag{11}$$

where (11) ensures that each task  $\tau_i$  is assigned to a core.

2) Frequency Assignment Constraints: Since all cores and links in the target platform support DVFS, for each core and link, we have

$$\sum_{k \in \mathcal{N}_p} c_{i,k}^P = 1, \ \forall i \in \mathcal{N},$$

(12)

$$\sum_{g \in \mathcal{N}_i} c_{i,j,g}^L = 1, \ \forall e_{i,j} \in \mathcal{E},$$

(13)

where (12) ensures that a task  $\tau_i$  is executed with one V/F core level  $(v_{p,k}, f_{p,k})$ , and (13) restricts that the message of edge  $e_{i,j}$  is transmitted with one V/F link level  $(v_{l,q}, f_{l,q})$ .

3) Communication Start Time Constraints: The message transmission for edges should consider the precedence relations. For example, in Fig. 1(b), when the message for edge  $e_{i,j}$  is transmitted from task  $\tau_i$  to  $\tau_j$ , the communication start time  $ts_{i,j}$  is not earlier than the finish time of the predecessor  $\tau_i$ . Therefore, we have

$$te_i \le ts_{i,j}, \ \forall e_{i,j} \in \mathcal{E}.$$

(14)

4) Communication End Time Constraints: Taking task allocation and DVFS on links during task scheduling into account, the communication time of message  $e_{i,j}$  is represented as

$$t_{i,j}^{L} = \left(\sum_{s \in \mathcal{M}} \sum_{d \in \mathcal{M}} h_{s,d} x_{i,s} x_{j,d}\right) \sum_{g \in \mathcal{N}_l} c_{i,j,g}^{L} t_{i,j,g}^{UL},$$

(15)

where  $\sum_{g \in \mathcal{N}_l} c_{i,j,g}^L t_{i,j,g}^{UL}$  represents the transmission time over one unit link with DVFS, and  $\sum_{s \in \mathcal{M}} \sum_{d \in \mathcal{M}} h_{s,d} x_{i,s} x_{j,d}$  is the number of links when transmitting the message for edge  $e_{i,j}$ .

If the message transmits from  $\tau_i$  to  $\tau_j$  through  $e_{i,j}$ , the communication end time  $te_{i,j}$  is equal to the sum of communication

TABLE II

MAIN NOTATIONS USED IN PROBLEM FORMULATIONS

| Related | Parameters |

|---------|------------|

| N       | number     |

$\begin{array}{ll} N & \text{number of tasks in set } \mathcal{T} \triangleq \{\tau_i, \dots, \tau_N\}. \\ M & \text{number of cores in set } \mathcal{P} \triangleq \{P_1, \dots, P_M\}. \\ \mathcal{R} & \text{router sets, where } \mathcal{R} \triangleq \{R_1, \dots, R_M\}. \\ l_{s,d} & \text{physical link between cores } P_s \text{ and } P_d. \\ \end{array}$

$\mathcal{L}_{s,d}$  routing set between cores  $P_s$  and  $P_d$ .

Manhattan distance between core  $P_s$  and  $P_d$ .

$(v_{p,k}, f_{p,k})$  the  $k^{th}$  V/F level of core.  $(v_{l,g}, f_{l,g})$  the  $g^{th}$  V/F level of link.

$N_p(N_l)$  number of V/F levels in cores (links).

$b_{\omega}$  link bandwidth.

$\begin{array}{ll} e_{i,j} & \text{dependency between tasks } \tau_i \text{ and } \tau_j, \text{ where } e_{i,j} \in \mathcal{E}. \\ s_{i,j} & \text{size of communication data between tasks } \tau_i \text{ and } \tau_j. \end{array}$

$\omega_i$  execution cycles of task  $\tau_i$ .  $D_i$  task deadline of task  $\tau_i$ .

$\alpha_i$  = 1 if task  $\tau_i$  has no predecessors, else  $\alpha_i = 0$ .  $\lambda_0$ , d average fault rate and transient fault sensitivity.

$R_{th}$  reliability threshold.

weight in the objective function.

### **Binary Variables**

| $x_{i,s}$        | = 1 if task $\tau_i$ is assigned to core $P_s$ , else $x_{i,s} = 0$ .  |

|------------------|------------------------------------------------------------------------|

| $c_{i,k}^P$      | = 1 if task $\tau_i$ is executed with V/F level $(v_{p,k}, f_{p,k})$ , |

| $c_{i,k}$        | else $c_{i,k}^P = 0$ .                                                 |

| $_{\circ}L$      | = 1 if the message for edge $e_{i,j}$ is transmitted with              |

| $c_{i,j,g}^L$    | the level V/F $(v_{l,q}, f_{l,q})$ , else $c_{i,j,q}^L = 0$ .          |

|                  | = 1 if task $\tau_i$ starts execution before $\tau_j$ is completed,    |

| $o_{i,j}$        | else $o_{i,j} = 0$ .                                                   |

| m                | = 1 if edge $e_{i,j}$ starts transmitting messages                     |

| $\eta_{i,j,m,n}$ | before $e_{m,n}$ completes, else $\eta_{i,j,m,n} = 0$ .                |

#### **Continuous Variables**

| $ts_i$ $(te_i)$   | start (end) time of executing $\tau_i$ .                      |

|-------------------|---------------------------------------------------------------|

|                   | start (end) time of message transmission for edge $e_{i,j}$ . |

| $t_{i,j}^{slack}$ | slack time for edge $e_{i,j}$ .                               |

| $U_{ m max}$      | maximum core utilization rate.                                |

#### **Auxiliary Variables**

| $\beta_{i,s,k}$      | binary variable, and $\beta_{i,s,k} = x_{i,s} c_{i,k}^P$ .                 |

|----------------------|----------------------------------------------------------------------------|

| $\gamma_{i,j,s,d}$   | binary variable, and $\gamma_{i,j,s,d} = x_{i,s} x_{j,d}$ .                |

| $\delta_{i,j,s,d,g}$ | binary variable, and $\delta_{i,j,s,d,g} = \gamma_{i,j,s,d} c_{i,j,g}^L$ . |

start time  $ts_{i,j}$ , communication time  $t_{i,j}^L$ , and slack time  $t_{i,j}^{slack}$ . The value of  $te_{i,j}$  is not earlier than the start time of the successor  $\tau_j$ . Thus, we have

$$te_{i,j} = ts_{i,j} + t_{i,j}^L + t_{i,j}^{slack} \le ts_j, \ \forall e_{i,j} \in \mathcal{E}.$$

(16)

5) Real-time Constraints: For the real-time tasks, since each task  $\tau_j$  must be completed within the deadline  $D_j$ , we have

$$te_j = ts_j + \sum_{k \in \mathcal{N}_n} c_{j,k}^P t_{j,k}^P \le D_j, \ \forall j \in \mathcal{N},$$

(17)

where  $\sum_{k \in \mathcal{N}_p} c_{j,k}^P t_{j,k}^P$  is the execution time of  $\tau_j$  with DVFS. 6) Task Non-overlapping Constraints: If tasks are assigned to the same core, their execution sequence should be determined since one core cannot execute multiple tasks at the same time. Hence, we have the following constraints:

$$(te_j - ts_i)/Z \le o_{i,j} \le (te_j - ts_i)/Z + 1,$$

(18)

$$o_{i,j} + o_{j,i} + x_{i,s} + x_{j,s} \le 3, \ \forall e_{i,j} \notin \mathcal{E}, \ \forall s \in \mathcal{M}.$$

(19)

If task  $\tau_i$  starts the execution before the completion of task  $\tau_j$ , i.e.,  $ts_i \leq te_j$ , (18) is transformed to  $o_{i,j}=1$ , otherwise, we get  $o_{i,j}=0$ . If the execution time of  $\tau_i$  and  $\tau_j$  overlaps, and there is no dependency between  $\tau_i$  and  $\tau_j$ ,  $ts_j \leq te_i$  and  $ts_i \leq te_j$  hold. We get  $o_{i,j}=o_{j,i}=1$  from (18). Therefore, (19) is transformed to  $x_{i,s}+x_{j,s}\leq 1$ , which means  $\tau_i$  and  $\tau_j$  cannot be assigned to the same core.

7) Reliability Constraints: Note that we consider transient faults on both cores and links. On the one hand, we consider only faults on cores for the task without predecessors, as there is no communication between this task and its predecessors. Let parameter  $\alpha_j = 1$  denote task  $\tau_j$  does not have predecessors, otherwise,  $\alpha_j = 0$ . With  $\alpha_j = 1$  and DVFS, the reliability probability of task  $\tau_j$  is given by

$$R_j = \sum_{k \in \mathcal{N}_p} c_{j,k}^P r_{j,k}^P, \ \forall j \in \mathcal{N}, \ \alpha_j = 1.$$

(20)

On the other hand, if task  $\tau_j$  has predecessors, i.e.,  $\alpha_j = 0$ , we consider the reliability on both cores and links. Since the reliability of each link is related to the V/F, the reliability probability of links transmitting  $e_{i,j}$  with DVFS is  $\sum_{g \in \mathcal{N}_l} c_{i,j,g}^L r_{i,j,g}^L$ . Therefore, the reliability probability of task  $\tau_j$  is calculated as

$$R_{j} = \left(\sum_{k \in \mathcal{N}_{p}} c_{j,k}^{P} r_{j,k}^{P}\right) \prod_{e_{i,j} \in \mathcal{E}} \left(\sum_{g \in \mathcal{N}_{l}} c_{i,j,g}^{L} r_{i,j,g}^{L}\right),$$

$$\forall j \in \mathcal{N}, \ \alpha_{j} = 0. \quad (21)$$

Combining (20) and (21), the reliability probability of task  $\tau_j$ , including computation and communication, is formulated as:

$$R_{j} = \begin{cases} \sum_{k \in \mathcal{N}_{p}} c_{j,k}^{P} r_{j,k}^{P}, \ \forall j \in \mathcal{N}, \ \alpha_{j} = 1, \\ \left(\sum_{k \in \mathcal{N}_{p}} c_{j,k}^{P} r_{j,k}^{P}\right) \prod_{e_{i,j} \in \mathcal{E}} \left(\sum_{g \in \mathcal{N}_{l}} c_{i,j,g}^{L} r_{i,j,g}^{L}\right), \\ \forall j \in \mathcal{N}, \ \alpha_{j} = 0. \end{cases}$$

(22)

To run applications successfully, we must consider the reliability requirements of scheduling and routing for all tasks. Thus, the joint reliability probability of each task  $\tau_j$  should be larger than reliability threshold  $R_{th}$ , and we have

$$R_i \ge R_{th}, \ \forall j \in \mathcal{N}.$$

(23)

8) Utilization Balance Constraints: Imbalanced mapping of tasks harms system reliability since the cores with heavy tasks assigned have high circuit activities, which raises the average fault rate  $\lambda_0$  and decreases system reliability [22]. Moreover, load imbalance may cause local congestion in NoC, and the increased transmission delay will degrade communication efficiency. To improve system performance, we consider a load-balanced task mapping to minimize the maximum core utilization rate  $U_{\rm max}$ . To restrict the maximum core utilization rate among the cores, we have the following constraints:

$$U_{s} = \underbrace{\left(\sum_{i \in \mathcal{N}} \sum_{k \in \mathcal{N}_{p}} x_{i,s} c_{i,k}^{P} t_{i,k}^{P}\right)}_{\text{(a)}} / H \le U_{\text{max}}, \ \forall s \in \mathcal{M},$$

(24)

where  $U_s$  denotes the core utilization rate of  $P_s$ , given by the ratio of the total task execution time on core  $P_s$  (i.e., (24)-(a)) to the scheduling horizon H.

9) Objective Function: We aim to minimize the weighted core utilization rate and total energy consumption. The objective function can be formulated as follows:

$$\min \mu E_{total} / E_{\text{max}} + (1 - \mu) U_{\text{max}}. \tag{25}$$

where  $\mu \in [0,1]$  is a weighted factor,  $E_{total}$  is the total energy consumption, and  $E_{max}$  is an upper bound of  $E_{total}$ .

$$E_{total} = \sum_{e_{i,j} \in \mathcal{E}} \sum_{s \in \mathcal{M}} \sum_{d \in \mathcal{M}} x_{i,s} x_{j,d} s_{i,j} [(h_{s,d} + 1) E_{Rbit} + h_{s,d} \sum_{g \in \mathcal{N}_l} c_{i,j,g}^L E_{Lbit,g}] + \sum_{i \in \mathcal{N}} \sum_{k \in \mathcal{N}_p} c_{i,k}^P P_k^{comp} t_{i,k}^P.$$

(26)

10) Primal Problem: Based on the above constraints and objective function, the contention- and reliability-aware task mapping problem is formulated as follows:

$$\mathbf{PP}: \min_{\substack{x, c^P, c^L, o, \eta, \\ t^P + t^L + \mu}} \mu E_{total} / E_{max} + (1 - \mu) U_{max}$$

(27)

$$\text{s.t.} \begin{cases} (5) - (7), (11) - (19), (22) - (24), \\ x_{i,s}, c_{i,k}^P, c_{i,j,g}^L, o_{i,j}, \eta_{i,j,m,n} \in \{0,1\}, \ 0 \leq ts_i, ts_{i,j} \leq H, \\ \forall i, j, m, n \in \mathcal{N}, \ \forall s \in \mathcal{M}, \ \forall k \in \mathcal{N}_p, \ \forall g \in \mathcal{N}_l, \end{cases}$$

where we have  $\boldsymbol{x} = [x_{i,s}]_{N\times M}$ ,  $\boldsymbol{c}^P = [c_{i,k}^P]_{N\times N_p}$ ,  $\boldsymbol{c}^L = [c_{i,j,g}^L]_{N\times N\times N_l}$ ,  $\boldsymbol{o} = [o_{i,j}]_{N\times N}$ ,  $\boldsymbol{\eta} = [\eta_{i,j,m,n}]_{N\times N\times N\times N}$ ,  $\boldsymbol{ts}^P = [ts_i]_{1\times N}$ ,  $\boldsymbol{ts}^L = [ts_{i,j}]_{N\times N}$ ,  $\boldsymbol{t} = [t_{i,j}^{slack}]_{N\times N}$ , and  $\boldsymbol{u} = U_{\max}$ . Note that  $\boldsymbol{x}$ ,  $\boldsymbol{c}^P$ ,  $\boldsymbol{c}^L$ ,  $\boldsymbol{o}$ , and  $\boldsymbol{\eta}$  are binary variables, while  $\boldsymbol{ts}^P$ ,  $\boldsymbol{ts}^L$ ,  $\boldsymbol{t}$ , and  $\boldsymbol{u}$  are continuous variables. Moreover, the nonlinear terms  $e^{-\lambda t}$ ,  $x_{i,s}c_{i,k}^P$ , and  $x_{i,s}x_{j,d}c_{i,j,g}^L$  are included in (15), (23), (24) and (26). Thus, (27) is an MINLP problem.

Remark 3.1: DVFS switching overheads are mainly influenced by the V/F levels before and after transition [37]. The time overhead is  $t^{switch}(f_s,f_e)=t_{trans}\times(f_e-f_s)/f_e$ , and the energy overhead is  $E^{switch}(f_s,f_e)=P_s^{switch}\times t^{switch}(f_s,f_e)$ , where  $t_{trans}$  is a time transition parameter,  $f_s$  and  $f_e$  are the frequencies before and after transition, respectively, and  $P_s^{switch}$  is the power before frequency transition. Based on the parameters of the NoC platform, we can get switching overheads regarding the links and the cores, e.g.,  $t_{i,j}^{Lswitch}$  and  $E_{i,j}^{Lswitch}$  for data transmission among the edge  $e_{i,j}$ , and  $t_i^{Pswitch}$  and  $E_i^{Pswitch}$  for execution of task  $\tau_i$ . Considering the DVFS switching overhead in PP, the extra time  $(t_{i,j}^{Lswitch})$  and energy  $(E_{i,j}^{Lswitch})$  and  $E_i^{Pswitch}$  and  $E_i^{Pswitch}$  and energy  $(E_{i,j}^{Lswitch})$  and (26).

Remark 3.2: In (2), the leakage current  $I_{sub}$  is affected by temperature T. The relationship between them can be described by a complex nonlinear function [38]. To reduce complexity, the leakage current can be linearized with the temperature within a given acceptable accuracy [16], [20], [27]. Specifically, the static power working at the V/F level  $(v_{p,k},f_{p,k})$  can be modeled as  $P_{sta,k}^{comp} = (\gamma_s + \eta_s T) \times v_{p,k}$ , where  $\gamma_s$  and  $\eta_s$  are constants depending on core  $P_s$ . Let T(t) denote the temperature at time t. In (26), the energy consumed by the static power can be updated to  $\sum_{s \in \mathcal{M}} \sum_{i \in \mathcal{N}} \sum_{k \in \mathcal{N}_p} x_{i,s} c_{i,k}^P t_{i,k}^P v_{p,k} (\gamma_s + \eta_s \int_0^H T(t) dt)$ . Remark 3.3: The above problem can be extended to hetero-

Remark 3.3: The above problem can be extended to heterogeneous platforms by modifying the constraints (12), (17), (22), (24), and (26). In addition, we can replace the frequency assignment variable  $c_{i,k}^P$  with  $c_{i,s,k}^P$ , where  $c_{i,s,k}^P = 1$  denotes that task

$\tau_i$  assigned to core  $P_s$  is executed with V/F level  $(v_{s,k}^P, f_{s,k}^P)$ . Similarly, the execution time of  $\tau_i$  on  $P_s$  with  $(v_{s,k}^P, f_{s,k}^P)$  is updated as  $t_{i,s,k}^P = \omega_i/f_{s,k}^P$ , and the reliability of executing  $\tau_i$  on  $P_s$  with  $(v_{s,k}^P, f_{s,k}^P)$  is represented as  $r_{i,s,k}^P = e^{-\lambda_P \times f_{s,k}^P \times t_{i,s,k}^P}$ .

#### C. Problem Linearization

The MINLP problem has been proven to be an NP-Hard [39], which is hard to solve within polynomial time. To find the optimal solution to PP, we propose a linearization method, which can equivalently convert PP into an MILP problem.

1) Nonlinear terms caused by exponential terms: We introduce the following lemma to linearize the product of binary variables and exponential terms in (23).

Lemma 3.1: Assume that  $z_i$  is a binary variable, and the constant  $a_i > 0$  for each  $i \in \mathcal{N}$ . When  $\sum_{i \in \mathcal{N}} z_i = 1$ , the equation  $\ln(\sum_{i \in \mathcal{N}} a_i z_i) = \sum_{i \in \mathcal{N}} z_i \ln a_i$  holds.

Proof: Considering the case when binary variable  $z_m=1$ , while the other binary variable  $z_n=0$  ( $\forall n\neq m\in\mathcal{N}$ ) due to  $\sum_{i\in\mathcal{N}}z_i=1$ . Therefore, we have  $\ln(\sum_{i\in\mathcal{N}}a_iz_i)=\ln(a_1\times 0+\cdots+a_mz_m+\cdots+a_N\times 0)=\ln a_mz_m=\ln a_m$ . On the other hand, we get  $\sum_{i\in\mathcal{N}}z_i\ln a_i=0\times\ln a_1+\cdots+z_m\ln a_m+\cdots+0\times a_N=z_m\ln a_m=\ln a_m$ . Therefore, it is proved that  $\ln(\sum_{i\in\mathcal{N}}a_iz_i)=\sum_{i\in\mathcal{N}}z_i\ln a_i$  when  $\sum_{i\in\mathcal{N}}z_i=1$ .

Since logarithm is a monotonically increasing function, the relation between left and right parts in (23) remains unchanged when logarithm operation is performed on both sides of (23). According to *Lemma* 3.1, (23) can be linearized as follows:

$$ln R_j \ge ln R_{th}, \ \forall j \in \mathcal{N},$$

(28)

where

$$\begin{split} & \ln R_j = \\ & \left\{ \sum_{k \in \mathcal{N}_p} c_{j,k}^P \ln r_{j,k}^P, \ \alpha_j = 1, \\ & \sum_{e_{i,j} \in \mathcal{E}} \sum_{g \in \mathcal{N}_l} c_{i,j,g}^L \ln r_{i,j,g}^L + \sum_{k \in \mathcal{N}_p} c_{j,k}^P \ln r_{j,k}^P, \ \alpha_j = 0, \\ & \ln r_{j,k}^P = \ln e^{-\lambda_P(f_{p,k}) \times t_{j,k}^P} = -\frac{\omega_j \lambda_P(f_{p,k})}{f_{p,k}}, \\ & \ln r_{i,j,g}^L = \sum_{s \in \mathcal{M}} \sum_{d \in \mathcal{M}} x_{i,s} x_{j,d} h_{s,d} \ln r_{i,j,g}^{UL} \\ & = -\sum_{s \in \mathcal{M}} \sum_{d \in \mathcal{M}} x_{i,s} x_{j,d} \frac{h_{s,d} s_{i,j} \lambda_L(f_{l,g})}{b_\omega f_{l,g}}. \end{split}$$

Taking the value of  $\alpha_j$  in the above equations into account, (28) can be reformulated as follows:

$$\ln R_{j} = (1 - \alpha_{j}) \sum_{e_{i,j} \in \mathcal{E}} \sum_{g \in \mathcal{N}_{l}} c_{i,j,g}^{L} \ln r_{i,j,g}^{L}$$

$$+ \sum_{k \in \mathcal{N}_{p}} c_{j,k}^{P} \ln r_{j,k}^{P} \ge \ln R_{th}, \ \forall j \in \mathcal{N}. \quad (29)$$

2) Nonlinear terms caused by the products of binary variables: We propose the following lemma to tackle the nonlinear items  $x_{i,s}c_{i,k}^P$  and  $x_{i,s}x_{j,d}c_{i,j,g}^L$  in (15), (24), (26), and (29).

Lemma 3.2: Assume that  $x_1$  and  $x_2$  are binary variables. The nonlinear term  $x_1x_2$  can be replaced by an auxiliary (binary) variable y, where  $y = x_1x_2$ , and the additional constraints  $y \le x_1$ ,  $y \le x_2$  and  $y \ge x_1 + x_2 - 1$ .

*Proof:* When binary variables  $x_1 = 1$  and  $x_2 = 1$ , the additional constraint is transformed to  $1 \le y \le 1$ , i.e., y = 1

holds. Similarly, for the cases 1)  $x_1 = 0$  and  $x_2 = 0$ ; 2)  $x_1 = 1$  and  $x_2 = 0$ ; 3)  $x_1 = 0$  and  $x_2 = 1$ , we have  $y = x_1x_2 = 0$ .

Based on *Lemma* 3.2, we introduce auxiliary (binary) variables  $\beta_{i,s,k}$ ,  $\gamma_{i,j,s,d}$  and  $\delta_{i,j,s,d,g}$  to replace the nonlinear items, where  $\beta_{i,s,k} = x_{i,s}c_{i,k}^P$ ,  $\gamma_{i,j,s,d} = x_{i,s}x_{j,d}$ , and  $\delta_{i,j,s,d,g} = \gamma_{i,j,s,d}c_{i,j,g}^L$ , and add the following constraints into (27).

$$\forall i, j \in \mathcal{N}, \ \forall s, d \in \mathcal{M}, \ \forall k \in \mathcal{N}_p, \ \forall g \in \mathcal{N}_l,$$

$$\beta_{i,s,k} \leq x_{i,s}, \beta_{i,s,k} \leq c_{i,k}^P, \beta_{i,s,k} \geq x_{i,s} + c_{i,k}^P - 1, \qquad (30)$$

$$\gamma_{i,j,s,d} \leq x_{i,s}, \gamma_{i,j,s,d} \leq x_{j,d}, \gamma_{i,j,s,d} \geq x_{i,s} + x_{j,d} - 1, \qquad (31)$$

$$\delta_{i,j,s,d,g} \leq \gamma_{i,j,s,d}, \delta_{i,j,s,d,g} \leq c_{i,j,g}^L,$$

$$\delta_{i,j,s,d,g} \geq \gamma_{i,j,s,d} + c_{i,j,g}^L - 1. \qquad (32)$$

Thus, the primal problem (27) can be converted into the following MILP problem through the above linearization method.

$$\begin{aligned} & \mathbf{PP1} : \min_{\substack{x,c^P,c^L,o,\eta,ts^P,\\ts^L,t,u,\beta,\gamma,\delta}} \mu E_{total} / E_{max} + (1-\mu) U_{max} \end{aligned}$$

(3)

$$\mathbf{s.t.} \begin{cases} & (5) - (7), \ (11) - (14), (16) - (19), (29) - (32),\\ & t_{i,j}^L = \sum_{s \in \mathcal{M}} \sum_{d \in \mathcal{M}} \sum_{g \in \mathcal{N}_l} h_{s,d} \delta_{i,j,s,d,g} t_{i,j,g}^{UL},\\ & U_s = \left(\sum_{i \in \mathcal{N}} \sum_{k \in \mathcal{N}_p} \beta_{i,s,k} t_{i,k}^P\right) / H \leq U_{\max},\\ & x_{i,s}, c_{i,k}^P, c_{i,j,g}^L, o_{i,j}, \eta_{i,j,m,n}, \beta_{i,s,k}, \gamma_{i,j,s,d},\\ & \delta_{i,j,s,d,g} \in \{0,1\}, \ 0 \leq ts_i, ts_{i,j} \leq H,\\ & \forall i,j,m,n \in \mathcal{N}, \ \forall s,d \in \mathcal{M}, \ \forall k \in \mathcal{N}_p, \ \forall g \in \mathcal{N}_l, \end{aligned}$$

where we set  $\boldsymbol{\beta} = [\beta_{i,s,k}]_{N \times M \times N_p}$ ,  $\boldsymbol{\gamma} = [\gamma_{i,j,s,d}]_{N \times N \times M \times M}$ , and  $\boldsymbol{\delta} = [\delta_{i,j,s,d,g}]_{N \times N \times M \times M \times M_l}$ , and the total energy consumption  $E_{total}$  in the objective function of (33) is given by  $E_{total} = \sum_{e_{i,j} \in \mathcal{E}} \sum_{s \in \mathcal{M}} \sum_{d \in \mathcal{M}} s_{i,j} [(h_{s,d}+1)\gamma_{i,j,s,d} E_{Rbit} + h_{s,d} \sum_{g \in \mathcal{N}_l} \delta_{i,j,s,d,g} E_{Lbit,g}] + \sum_{i \in \mathcal{N}} \sum_{k \in \mathcal{N}_p} c_{i,k}^P P_k^{comp} t_{i,k}^P.$

## IV. HEURISTIC TASK MAPPING APPROACH

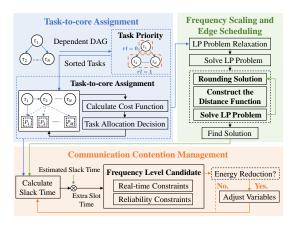

The proposed contention- and reliability-aware task mapping problem can be transformed into an MILP problem using the linearization methods presented in Section III-C. However, only small-scale problems can be solved efficiently by optimization solvers, such as Gurobi and CPLEX. The problem with large scale will lead to excessive time consumption and memory overflow problems. Hence, we proposed a novel three-step Contention- and Reliability-Aware Task Mapping and Scheduling (CRATMS) heuristic to perform 1) task-to-core assignment, 2) frequency scaling and edge scheduling, and 3) communication contention management, so as to provide better system performance. The structure of CRATMS is shown in Fig. 2.

### A. Task Allocation Scheme

Since the tasks are dependent, the task-to-core assignment directly affects task scheduling and communication on NoC. In addition, the task allocation variable x exists in all the constraints of PP except the frequency assignment constraints (12) and (13), and thus, we consider x at the first step. The optimization processes are summarized in Algorithm 1.

Fig. 2. The structure of the proposed CRATMS scheme.

- 1) Task Priority: We introduce the concept of task level to sort the dependent tasks in DAG. The task level of task  $\tau_i$  is defined as the largest number of edges from itself to the entry node:  $rl(\tau_j) = \max_{\forall e_{i,j} \in \mathcal{E}} \{rl(\tau_i)\} + 1$ , and we set the task level of entry nodes as zero. For example, in Fig. 1(a), we have  $rl(\tau_a) = 0$ ,  $rl(\tau_b) = 1$ ,  $rl(\tau_v) = 1$ ,  $rl(\tau_m) = 1$ ,  $rl(\tau_i) = 2$ ,  $rl(\tau_j) = 3$ ,  $rl(\tau_n) = 3$ ,  $rl(\tau_u) = 4$ , and  $rl(\tau_w) = 5$ . Therefore, the tasks in the set  $\mathcal{T}$  can be sorted in ascending order according to their task levels, and we can get a new task set  $\widehat{\mathcal{T}}$  (Line 2).

- 2) Task-to-core Assignment: To reduce the routing costs while balancing the task workloads among the cores, we consider the cost function of task  $\tau_j$  assigned to core  $P_d$  as follows:

$$F(\tau_{j}, P_{d}) = \underbrace{\left(\mu \sum_{e_{i,j} \in \mathcal{E}} \sum_{s \in \mathcal{M}} x_{i,s} h_{s,d}\right) / h_{\max}}_{\text{(a)}} + \underbrace{\left(1 - \mu\right) \left(U_{d} + t_{j,\min}^{P} / H\right)}_{\text{(b)}} \quad (34)$$

where  $h_{\max}$  is the maximum Manhattan distance on NoC through the XY routing, and  $t_{j,\min}^P$  is the execution time of task  $\tau_j$  on core  $P_d$  with the minimum frequency  $f_{p,\min}$ . Hence, (34)-(a) is the ratio of routing distances between the cores executing tasks  $\tau_i$  and  $\tau_j$  to the maximum distance  $h_{\max}$ , and (34)-(b) is the core utilization of  $P_d$ . To reduce the cost of task assignment, for each non-entry task  $\tau_j$ , they are assigned to the core  $P_{d^*}$  with the minimum cost function, i.e.,  $d^* = \arg\min_{d \in \mathcal{M}} F(\tau_j, P_d)$  (Line 5). However, since the entry tasks do not have predecessors, we assume that these tasks are assigned to core  $P_1$ , i.e.,  $d^* = 1$  (Line 7). After completing the assignment of task  $\tau_j$ , we can update the task assignment decision  $x_{j,d^*} = 1$  (Line 9) and core utilization rate  $U_d = U_d + t_{j,\min}^P/H$  (Line 10). The decision regarding task allocation  $x^*$  is determined by applying the above method for each task.

## B. Frequency Scaling and Edge Scheduling

Under the given task allocation decision, the frequencies of cores and links relate to energy consumption, task reliability, and real-time constraints, affecting the starting and ending time of task execution and edge communication. Therefore, the variables regarding core frequency assignment  $c^P$ , link frequency assignment  $c^L$ , task sequence o, start time of task execution

### Algorithm 1: Task Allocation Scheme

```

Input: Task graph TG and 2D-mesh NoC with M cores Output: Task allocation variable \boldsymbol{x}^*

1 Initialize x_{j,d} = 0 and U_d = 0 (\forall j \in \mathcal{N}, \forall d \in \mathcal{M});

2 Sort tasks in \mathcal{T} by ascending task levels, and get \widehat{\mathcal{T}};

3 for each task \tau_j in \widehat{\mathcal{T}} do

4 | if rl(\tau_j) \neq 0 then

5 | Get d^* = \arg\min_{d \in \mathcal{M}} F(\tau_j, P_d) through (34);

6 else

7 | Set d^* = 1;

8 end

9 Assign task \tau_j to core P_{d^*}, and set x_{j,d^*} = 1;

10 Update U_{d^*} = U_{d^*} + t_{j,min}^P/H;

```

$ts^P$  and start time of message transmission  $ts^L$  are determined at this step concurrently. However, according to (7), the coupling between the slack time t and other variables, e.g., x,  $c^L$ ,  $ts^P$ , and  $ts^L$  makes it challenging to solve the problem of frequency scaling and edge scheduling. To handle this problem, we assume that the slack time t has a predetermined value  $\hat{t}$ , which is calculated from (7) in the worst case. In this case, the communication contention constraints for any two edges, e.g.,  $e_{i,j}$  and  $e_{m,n}$  in time are satisfied  $(\eta_{i,j,m,n} = \eta_{m,n,i,j} = 1)$ , and the link frequencies are set to the minimum frequency  $f_{l,\min}$ . Moreover, the objective function of (27) can be transformed to minimize the energy consumption on NoC since the core utilization rate has been determined in the first step. Thus, substituting  $x_{i,s}^*$  and  $\hat{t}_{i,j}^{slack}$  into (27), the problem of frequency scaling and edge scheduling is given by

SP1:

$$\min_{\boldsymbol{c}^{P}, \boldsymbol{c}^{L}, \boldsymbol{o}, t \boldsymbol{s}^{P}, t \boldsymbol{s}^{L}} E_{total}$$

(35)

s.t.

$$\begin{cases}

(12) - (19), (29), \\

c_{i,k}^{P}, c_{i,j,g}^{L}, o_{i,j} \in \{0, 1\}, \ 0 \leq t s_{i}, t s_{i,j} \leq H, \\

\forall i, j \in \mathcal{N}, \ \forall k \in \mathcal{N}_{p}, \ \forall g \in \mathcal{N}_{l}.

\end{cases}$$

Since (35) is an MILP problem with a smaller scale than (27), based on the structure of the problem, we proposed a novel Feasibility-Pump (FP) based method to solve it. The implementation details are summarized in Algorithm 2.

- I) Let  $\Phi = \{c^P, c^L, o, ts^P, ts^L\}$  denote the set of the variables in SP1, and we set  $\mathcal{I} = \{j | \phi_j \in \{0,1\}\}$ , where  $\phi_j$  is the  $j^{th}$  element in the set  $\Phi$ . To make problem (35) easier to solve, we relax it into a Linear Program (LP) problem SP2 by replacing the binary variables  $\{c^P, c^L, o\}$  with the continuous variables within the range [0,1] (Line 1). When SP2 is solved, we get the initial solution  $\Phi^{(0)*} = \{c^P, c^L, o, ts^P, ts^L\} \in \mathcal{Z}$  (Line 1), where  $\mathcal{Z}$  denotes the set of the feasible region of SP2.

- 2) We initialize the iteration number n=0 (Line 2). Since the values of  $\{\boldsymbol{c^P}, \boldsymbol{c^L}, \boldsymbol{o}\}$  in  $\Phi^{(0)}{}^*$  may not be integer, we round the values of  $\{\boldsymbol{c^P}, \boldsymbol{c^L}, \boldsymbol{o}\}$  to the nearest integers (Line 3). When considering the task-level DVFS, each task  $\tau_i$  is executed with only one V/F level on each core. Based on the  $i^{th}$  row of  $\boldsymbol{c^P}$ , we can find the maximum one among the values  $\{c_{i,1}^P, \dots, c_{i,N_p}^P\}$ , and denote it as  $k^* = \arg\max_{k \in \mathcal{N}_p} \{c_{i,k}^P\}$ . For task  $\tau_i$ , we assign the V/F level  $(v_{p,k^*}, f_{p,k^*})$  to execute this task. Therefore, we have  $\hat{c}_{i,k}^P = 1$   $(k = k^*)$  and  $\hat{c}_{i,k}^P = 0$   $(\forall k \neq k^* \in \mathcal{N}_p)$ . Similarly, we can handle the  $\boldsymbol{c^L}$  and  $\boldsymbol{o}$ .

## Algorithm 2: Frequency Scaling and Edge Scheduling

```

Input: Task allocation x and the predetermined slack time \hat{t} Output: Frequency assignment c^{P}* and c^{L}*, and the start time of execution (communication) ts^{P}* (ts^{L}*)

1 Relax SP1 to a LP problem and get the initial solution \Phi^{(0)}*;

Initialize iteration number n = 0;

Round \{m{c^P}, m{c^L}, m{o}\} in \Phi^{(0)}{}^* to \{m{\hat{c}^P}, m{\hat{c}^L}, m{\hat{o}}\}, and update the

solution \hat{\Phi}^{(0)} = \{\hat{\boldsymbol{c}}^{\boldsymbol{P}}, \hat{\boldsymbol{c}}^{\boldsymbol{L}}, \hat{\boldsymbol{o}}, t\boldsymbol{s}^{\boldsymbol{P}}, t\boldsymbol{s}^{\boldsymbol{L}}\};

while \Delta(\Phi^{(n)},\hat{\Phi}^{(n)})>0 and n< n_{\max} do

Solve \Phi^{(n)*} = \arg\min_{\Phi^{(n)}} \{ \Delta(\Phi^{(n)}, \hat{\Phi}^{(n)}) : \Phi^{(n)} \in \mathcal{Z} \};

if \Delta(\Phi^{(n)}, \hat{\Phi}^{(n)}) = 0 then

Find the solution to SP1 and return \Phi^{(n)}*;

Round \{c^P,c^L,o\} in {\Phi^{(n)}}^* to \{\hat{c}^P,\hat{c}^L,\hat{o}\}, and get

9

\begin{split} \hat{\Phi}^{(n)*} &= \{\hat{\boldsymbol{c}}^{\boldsymbol{P}}, \hat{\boldsymbol{c}}^{\boldsymbol{L}}, \hat{\boldsymbol{o}}, \boldsymbol{t}\boldsymbol{s}^{\boldsymbol{P}}, \boldsymbol{t}\boldsymbol{s}^{\boldsymbol{L}}\}; \\ \text{Set } \hat{\Phi}^{(n+1)} &= \hat{\Phi}^{(n)*} \text{ for the next iteration;} \end{split}

10

if \hat{\Phi}^{(n+1)} = \hat{\Phi}^{(n)} then

11

Select n_f variables \hat{\phi}_i (j \in \mathcal{I}) in \hat{\Phi}^{(n+1)} to flip their

12

values, and update \hat{\Phi}^{(n+1)};

13

end

14

Update iteration number n \to n+1;

15

end

16 end

if n=n_{\max}+1 and \Delta(\Phi^{(n)},\hat{\Phi}^{(n)})>0 then

17

Solve SP1 after substituting \{c^P, c^L, o\} with the corresponding

18

values in \hat{\Phi}^{(n)}, and get \Phi^{(n+1)^*};

while \Phi^{(n+1)^*} = \emptyset do

19

Update frequency levels with c_{i,k}^P=1 \rightarrow c_{i,k+1}^P=1 and

Solve SP1 after substituting \{c^P, c^L\} with the updated

21

values, and update \Phi^{(n+1)^*}

22

end

23 end

```

Specially, the rounding of  $o_{i,j}$  is given by  $\hat{o}_{i,j} = [o_{i,j}]$ , where  $[\cdot]$  represents the rounding operation. Therefore, the rounding processes of  $\{c^P, c^L, o\}$  are as follows:

$$\begin{cases} \hat{c}_{i,k}^{P} = 1, & \text{if } k = \arg\max\{c_{i,k}^{P}\}, & \text{else, } \hat{c}_{i,k}^{P} = 0, \\ \hat{c}_{i,j,g}^{L} = 1, & \text{if } g = \arg\max\{c_{i,j,g}^{L}\}, & \text{else, } \hat{c}_{i,j,g}^{L} = 0, \\ \hat{o}_{i,j} = [o_{i,j}], & \forall i, j \in \mathcal{N}, & \forall k \in \mathcal{N}_{p}, & \forall g \in \mathcal{N}_{l}. \end{cases}$$

(36)

According to (36), the values of  $\{c^P,c^L,o\}$  are transformed to  $\{\hat{c}^P,\hat{c}^L,\hat{o}\}$ , and the rounding result is  $\hat{\Phi}=\{\hat{c}^P,\hat{c}^P,\hat{o},ts^P,ts^L\}$  (Line 3). Note that there is no need to round the values of  $ts^P$  and  $ts^L$  as they are continuous. Therefore, we obtain  $\hat{\Phi}^{(0)}=\{\hat{c}^P,\hat{c}^P,\hat{o},ts^P,ts^L\}$ .

3) Note that  $\Phi^{(0)}{}^* = \{c^P, c^L, o, ts^P, ts^L\}$  is the solution to LP-based SP2. However, the values of  $\{c^P, c^L, o\}$  may not be integer. Although the values of  $\{\hat{c}^P, \hat{c}^L, \hat{o}\}$  in  $\hat{\Phi}^{(0)}$  are integer,  $\hat{\Phi}^{(0)}$  may not be the solution to SP2 as the constraints may be violated. Since SP2 is relaxed from SP1, they have the same set of constraints. If the values of  $\{c^P, c^L, o\}$  in  $\Phi^{(0)}{}^*$  are integer, SP1 and SP2 have the same solution. For the solution to SP1, besides the constraints in SP2 must be satisfied, the values of  $\{c^P, c^L, o\}$  should be the integer. To find the solution to SP1, based on the given rounding solution  $\hat{\Phi}$ , we construct a L1-norm distance between the solutions  $\Phi^* \in \mathcal{Z}$  and  $\hat{\Phi}$ , and we define it as  $\Delta(\Phi^*, \hat{\Phi}) = \sum_{j \in \mathcal{I}, \hat{\phi}_j = 1} (1 - \phi_j^*) + \sum_{j \in \mathcal{I}, \hat{\phi}_j = 0} \phi_j^*$ , where  $\hat{\phi}_j$  and  $\phi_j^*$  are the  $j^{th}$  elements in  $\hat{\Phi}$  and  $\Phi^*$ , respectively. Since  $\Delta(\Phi^*, \hat{\Phi}) \geq 0$ , we have the following two cases:

### Algorithm 3: Communication Contention Management

Input: The predetermined slack time  $\hat{\boldsymbol{t}}$  and the outputs of Algorithms 1 and 2

Output: Core frequency assignment  $c^{P^*}$ , the start time of executing tasks  $\boldsymbol{ts^{P^*}}$ , and the precise slack time  $\boldsymbol{t}^*$ 1 Update slack time  $t_{i,j}^{slack^*}$  ( $\forall e_{i,j} \in \mathcal{E}$ ) based on (5)-(7);

2 Calculate time slot  $\Delta t_{i,j} = \hat{t}_{i,j}^{slack} - t_{i,j}^{slack^*}$  ( $\forall e_{i,j} \in \mathcal{E}$ );

3 for each edge  $e_{i,j}$  in  $\mathcal{E}$  do

4 Initialize  $k_j^{init} = k$  for task  $\tau_j$  if  $c_{j,k}^{P^*} = 1$ ;

Calculate feasible frequency level  $\hat{k}_j = \max\{k_j^R, k_j^T\}$  through (38) and (39) for task  $\tau_j$ ;

if  $E_j^{comp}(f_{p,\hat{k}_j}) < E_j^{comp}(f_{p,k_j^{init}})$  then

7 Update  $c_{j,k}^{P^*} = 1$  ( $k = \hat{k}_j$ ) and  $c_{j,k}^{P^*} = 0$  ( $k \neq \hat{k}_j \in \mathcal{N}_p$ );

8 end

9 Calculate task start time  $ts_j^*$  by (17);

- a). If  $\Delta(\Phi^*, \hat{\Phi}) = 0$ ,  $\phi_j^*$  ( $\forall j \in \mathcal{I}$ ) is integer and  $\phi_j^* = \hat{\phi}_j$ , and thus,  $\Phi^*$  is a solution to SP1.

- b). If  $\Delta(\Phi^*, \hat{\Phi}) > 0$ , we round  $\Phi^*$  and update  $\hat{\Phi}$  with the rounding result. On this basis, to reduce the distance  $\Delta(\Phi^*, \hat{\Phi})$ , we update the values of  $\Phi^*$  and  $\hat{\Phi}$  iteratively until the distance  $\Delta(\Phi^*, \hat{\Phi}) = 0$ .

In the  $n^{th}$  iteration, to minimize  $\Delta(\Phi^{(n)}, \hat{\Phi}^{(n)})$  through  $\Phi^{(n)}$ , we construct a new problem SP3 as follows:

$$\mathbf{SP3} : \min_{\Phi^{(n)}} \Delta(\Phi^{(n)}, \hat{\Phi}^{(n)})$$

s.t.

$$\begin{cases} (12) - (19), (29), \\ c_{i,k}^{P}, c_{i,j,g}^{L}, o_{i,j} \in [0,1], \ 0 \le ts_{i}, ts_{i,j} \le H, \\ \forall i, j \in \mathcal{N}, \ \forall k \in \mathcal{N}_{p}, \ \forall g \in \mathcal{N}_{l}, \end{cases}$$

where  $\Phi^{(n)}$  and  $\hat{\Phi}^{(n)}$  denote the sets of variables and the rounding solution in the  $n^{th}$  iteration, respectively. Note that SP3 has the same form as SP2 except for the objective function. In the  $n^{th}$  iteration, we fix  $\hat{\Phi}^{(n)}$  and solve SP3 to obtain the solution  $\Phi^{(n)^*} \in \mathcal{Z}$ , so as to reduce the current distance  $\Delta(\Phi^{(n)},\hat{\Phi}^{(n)})$  (Line 5). If  $\Delta(\Phi^{(n)},\hat{\Phi}^{(n)})=0$ ,  $\Phi^{(n)^*}$  is the solution to SP1, and the iteration stops (Lines 6-7). Otherwise, we round the values of  $\{c^P,c^L,o\}$  in  $\Phi^{(n)^*}$  through (36), and get a rounding solution  $\hat{\Phi}^{(n)^*}$ , which is the given solution  $\hat{\Phi}^{(n+1)}=\hat{\Phi}^{(n)^*}$  in the  $(n+1)^{th}$  iteration (Lines 9-10).

Specially, if  $\hat{\Phi}^{(n+1)} = \hat{\Phi}^{(n)}$ , the solution to SP3 stays unchanged in the  $(n+1)^{th}$  iteration, which means the distance  $\Delta(\Phi^{(n+1)},\hat{\Phi}^{(n+1)})$  is unchanged as well. To avoid endless loop, we randomly select  $n_f$  elements, e.g.,  $\hat{\phi}_j \in \hat{\Phi}^{(n+1)}$   $(j \in \mathcal{I})$ , and flip their values (Lines 11-13), where  $n_f \in [N_F/2, 3N_F/4]$ , and  $N_F$  is a positive integer related to flipping number. During the flipping process, the value of  $\hat{\phi}_j$  is reset to 1 if  $\hat{\phi}_j = 0$ , otherwise,  $\hat{\phi}_j$  is reset to 0. Therefore, we can update  $\hat{\Phi}^{(n+1)}$  to avoid cycling issue (Line 12). Then, we update the iteration number  $n \to n+1$  (Line 14), and the iteration continues if  $\Delta(\Phi^{(n)},\hat{\Phi}^{(n)}) > 0$  or  $n < n_{\max}$ .

After iteration stops, we have  $n=n_{\rm max}+1$ . If the distance  $\Delta(\Phi^{(n)},\hat{\Phi}^{(n)})>0$ , the solution to SP1 is not founded, and we only get the rounding solution  $\hat{\Phi}^{(n)}$ . This solution cannot satisfy all constraints in SP1, especially the real-time and reliability constraints. Note that frequency assignment variables  $\{c^P,c^L\}$  have an influence on real-time constraints (17) and reliability

constraints (29). We iteratively adjust variables  $\{c^P, c^L\}$  based on the rounding solution  $\hat{\Phi}^{(n)}$  until the constraints in SP1 are satisfied (Lines 17-23). The details are as follows.

- a). Since the rounding solution  $\hat{\Phi}^{(n)}$  cannot satisfy the constraints in SP1, we solve SP1 by substituting  $\{c^P, c^L, o\}$  with the corresponding values in  $\hat{\Phi}^{(n)}$ . If this problem is feasible, we get a feasible solution  $\Phi^{(n+1)^*}$  (Line 18), i.e., the solution to SP1 is found, and the algorithm stops. Otherwise, we set the solution to SP1 as  $\Phi^{(n+1)^*} = \emptyset$ .

- b). When SP1 does not have a feasible solution, we increase the V/F levels of each core and link to find a feasible solution, e.g.,  $c_{i,k}^P=1 \rightarrow c_{i,k+1}^P=1$  and  $c_{i,j,g}^L=1 \rightarrow c_{i,j,g+1}^L=1$  (Line 20). That is because increased operation frequencies on cores and links can reduce task completion time and improve task reliability to satisfy real-time and reliability constraints.

- c). We update the values of  $\{c^P, c^L\}$  in SP1, and solve this problem to find the feasible solution  $\Phi^{(n+1)^*}$  (Line 21). Similarly, if SP1 dose not have a feasible solution, the solution  $\Phi^{(n+1)^*}$  is set to  $\emptyset$ .

- d). We check whether  $\Phi^{(n+1)^*} = \emptyset$ , in which case there is no feasible solution to SP1. We repeat Step b). and c). to adjust the frequencies on cores and links until the feasible solution  $\Phi^{(n+1)^*}$  is found, i.e.,  $\Phi^{(n+1)^*} \neq \emptyset$  (Lines 19-22).

By the above FP method, we get the solution to SP1, i.e.,  $\{c^{P^*}, c^{L^*}, o^*, ts^{P^*}, ts^{L^*}\}$ , but slack time  $\hat{t}$  is predetermined.

### C. Communication Contention Management

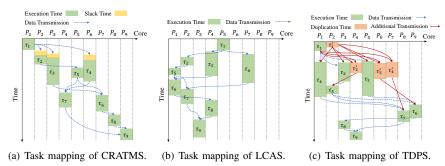

We apply Algorithm 2 to solve the problem of frequency scaling and edge scheduling and get the decisions regarding the core frequency assignment  $c^{P^*}$ , link frequency assignment  $c^{L^*}$ , task sequence  $o^*$ , task scheduling time  $ts^{P^*}$ , and edge scheduling time  $ts^{L^*}$ . In the worst case, they are based on the given slack time  $\hat{t}$ . During this process, we assume that the communication contention constraints in time are always satisfied, and the slack time  $\hat{t}$  is calculated with the minimum link frequency  $f_{\min}$ . Based on  $\{x^*, c^{L^*}, ts^{L^*}\}$ , we can update the slack time  $t^*$  through (5)-(7), and get the extra time slot  $\Delta t_{i,j} = \hat{t}_{i,j}^{slack} - t_{i,j}^{slack}, (\hat{t}_{i,j}^{slack} \in \hat{t}, t_{i,j}^{slack*} \in t^*)$ . Since  $\Delta t_{i,j}$  is a non-negative value, this time slot can execute task  $\tau_j$  or transmit data for the edge  $e_{i,j}$ . Lowering the operating frequency of the core/link, the system energy consumption can be further reduced. However, when  $\Delta t_{i,j}$  is used to transmit task data for the edge  $e_{i,j}$ , the start and end time of communication, i.e.,  $ts_{i,j}$  and  $te_{i,j}$  will be changed. Thus, the slack time  $t_{i,j}^{slack}$ is changed as well due to (5)-(7), which makes the problem difficult to solve. For problem-solving, we use time slot  $\Delta t_{i,j}$ for task execution. The details are summarized in Algorithm 3.

- a). We calculate the flexible slack time  $t_{i,j}^{slack*}$  according to  $\{x^*, c^{L^*}, ts^{L^*}\}$  for each edge  $e_{i,j} \in \mathcal{E}$  through (5)-(7) (Line 1). Based on the calculated slack time  $t_{i,j}^{slack*}$  and the predetermined slack time  $\hat{t}_{i,j}^{slack}$ , we can use extra slot time  $\Delta t_{i,j} = \hat{t}_{i,j}^{slack} t_{i,j}^{slack*}$  to execute task  $\tau_j$  (Line 2).

- b). After completing the communication for edge  $e_{i,j}$ , task  $\tau_j$  starts its execution. The initial frequency level used to execute  $\tau_j$  is set to  $k_j^{init} = k$  since  $c_{j,k}^{P} = 1$  (Line 4).

c). Since  $\Delta t_{i,j} \geq 0$  is only used for task execution, the execution time of  $\tau_j$  is extended from  $t_{j,k_j^{init}}^P$  to  $t_{j,k_j^{init}}^P + \Delta t_{i,j}$ . To satisfy the real-time constraints, the task start time  $ts_j$  can be ahead using the extra slot time  $\Delta t_{i,j}$ , while the task end time  $te_j$  remains unchanged. Considering the constraint of execution time for task  $\tau_j$ , the candidate of frequency level can be given by

$$k_j^T = \arg\max_{k \in \mathcal{N}_p} \{t_{j,k}^P : t_{j,k}^P \le t_{j,k_j^{init}}^P + \Delta t_{i,j}\},$$

(38)

where  $t_{j,k_j^{init}}^P$  denotes the execution time of task  $\tau_j$  with the frequency  $f_{p,k_j^{init}}$ . Besides task execution time, operated frequencies also influence task reliability due to (29). To satisfy the reliability constraints, the candidate frequency level can be set to

$$k_j^R = \arg\min_{k \in \mathcal{N}_p} \{ \ln r_{j,k}^P : \ln r_{j,k}^P + \ln R_j^L \ge \ln R_{th} \},$$

(39)

where  $R_j^L = \prod_{e_{i,j} \in \mathcal{E}} (\sum_{g \in \mathcal{N}_l} c_{i,j,g}^L {}^*r_{i,j,g}^L)$  denotes the reliability probability of communication between  $\tau_j$  and its predecessors, and  $r_{j,k}^P$  denotes the reliability probability of executing  $\tau_j$  with the frequency  $f_{p,k}$ . Therefore, to concurrently satisfy the constraints of task execution time and task reliability, the feasible frequency level for task  $\tau_j$  is set to  $\hat{k}_j = \max\{k_i^R, k_i^T\}$  (Line 5).

- d). To minimize energy consumption, we determine whether the update of execution frequency is necessary (Line 6). Under the given frequency  $f_{p,k}$ , the computation energy is  $E_j^{comp}(f_{p,k}) = P_k^{comp}t_{j,k}^P$ . For task  $\tau_j$ , if  $E_j^{comp}(f_{p,\hat{k}_j}) < E_j^{comp}(f_{p,k_j^{init}})$ , we set the execution frequency level as  $\hat{k}_j$ . Therefore, we update  $c_{j,k}^P = 1$   $(k = \hat{k}_j)$  and  $c_{j,k}^P = 0$   $(k \neq \hat{k}_j \in \mathcal{N}_p)$  (Line 7). On this basis, we can calculate task start time  $ts_j^*$  based on (17) (Line 9). However, if  $E_j^{comp}(f_{p,\hat{k}_j}) \geq E_j^{comp}(f_{p,k_j^{init}})$ , the frequency of  $\tau_j$  is unchanged since we aim to reduce energy consumption.

- e). We apply the above method for each edge  $e_{i,j} \in \mathcal{E}$  to update task execution frequency. Therefore, we can obtain the core frequency assignment  $c^{P^*}$ , the start time of executing tasks  $ts^{P^*}$ , and the flexible slack time  $t^*$ .

To sum up, through the above three algorithms: Task Allocation Algorithm 1, Frequency Scaling and Edge Scheduling Algorithm 2, and Communication Contention Algorithm 3, we can solve this task mapping and scheduling problem and obtain the solution  $\{x^*, c^{P^*}, c^{L^*}, o^*, ts^{P^*}, ts^{L^*}, t^*\}$ .

## D. Algorithm Complexity

CRATMS contains Algorithm 1-Algorithm 3, and the details of their computational complexities are as follows.

a). Task Allocation: A heuristic based on dynamic programming is applied in Algorithm 1 to solve the task allocation problem. Firstly, tasks are sorted according to their dependencies through the bubble method. The time complexity is  $O(N^2)$  when sorting N tasks [40]. Then, task-to-core assignment is conducted by the dynamic programming method. The number of sub-problems influences the time complexity. Since N tasks are assigned to processors for execution, the task assignment requires N iterations, and

TABLE III EXPERIMENTAL SET-UP

| Platform Model                                                                        |                                                                                                                   |                              |  |  |  |

|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|------------------------------|--|--|--|

| Platform Size $M: 2 \times 2 -$                                                       | $5 \times 5$ V/F Levels: $N_p = 5$ , $N_l = 5$                                                                    |                              |  |  |  |

| Processor Parameters                                                                  |                                                                                                                   |                              |  |  |  |

| Voltage $v_{p,k}$ (V)                                                                 | 0.75, 1.0, 1.3, 1.6, 1.8                                                                                          |                              |  |  |  |

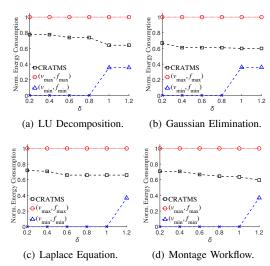

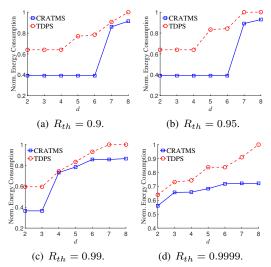

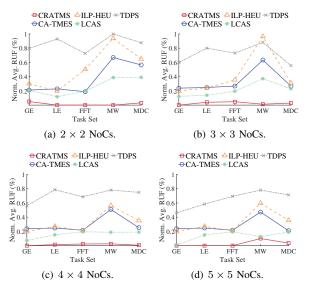

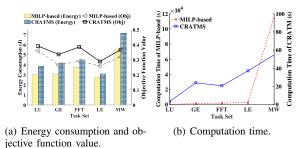

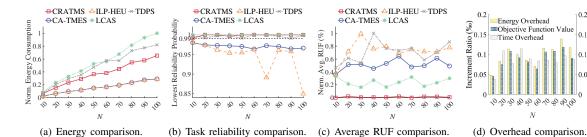

| Frequency $f_{p,k}$ (MHz)<br>Power $P_k^{comp}$ (mW)                                  | 150, 400, 600, 800, 1000                                                                                          |                              |  |  |  |